主题中讨论的其他器件:PMP22495、、 TL431

工具与软件:

你好

关于 PMP22495设计、我在使用 UCC2897A 的交流/直流应用中遇到了一个问题。 但这里我没有使用自动加载偏置、而是使用了控制器的辅助偏置。

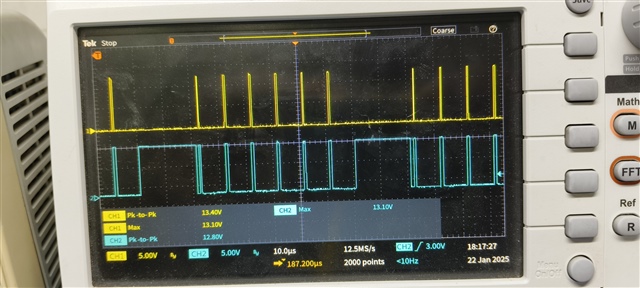

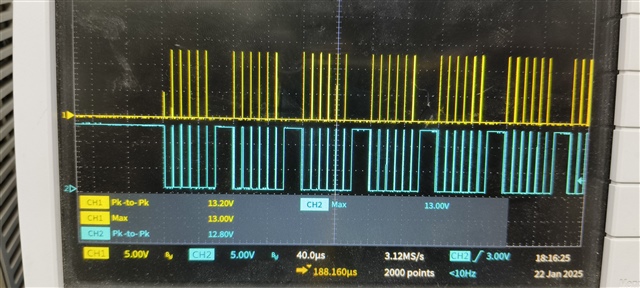

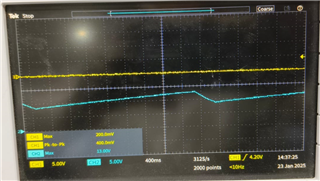

这是我观察到的波形、其中黄色位于 PMP22495中的 UCC5304D 输入端、辅助端、蓝色为主 MOSFET 的栅极。

此处、此应用是针对90VAC 至264VAC 设计的。

我将提供这些控制器

开关频率为100kHz、输出为15V/8A

变压器比 Np/Ns 为3.5、且偏置也是相同的比值

RDEL 为8.25K

Ron 为160K

ROFF 为240K

RSLOPE 为5K

VDD 为1uF

至于偏置绕组 VCC、电容器为320uF/50V

我通过基于发射极跟随器的线性稳压器直接从体电压提供 VIN。

我想主栅极脉冲很快关断、但 AUX 脉冲用于完整占空比。

请帮我解决这些问题。

谢谢你