工具与软件:

为了计算开关时序、我会搜索有关内部高侧驱动器的更多信息。

引脚等效图内部显示了使 FET "导通"的内部 FET。 该驱动器的电阻值是多少。

驱动 FET 时到 CHG 和 DSG 引脚的最小串联(GATE)电阻是多少? 我可以在不损坏 BQ 芯片的情况下放置0r 吗?

我知道快速开关还有其他问题、但我想了解 BQ 芯片能够提供的最大可能值。

谢谢

BR

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

工具与软件:

为了计算开关时序、我会搜索有关内部高侧驱动器的更多信息。

引脚等效图内部显示了使 FET "导通"的内部 FET。 该驱动器的电阻值是多少。

驱动 FET 时到 CHG 和 DSG 引脚的最小串联(GATE)电阻是多少? 我可以在不损坏 BQ 芯片的情况下放置0r 吗?

我知道快速开关还有其他问题、但我想了解 BQ 芯片能够提供的最大可能值。

谢谢

BR

您好、Max:

引脚等效图显示了我们无法表征共享的内部的简化电路。

您可以将一个0r 串联到 DSG/CHG 引脚、如所示 图5-11. FET 原理图 BQ76952EVM 用户指南中的说明。

第16.5节 FET 驱动器关断 和中提供 第6节 CHG 驱动器 和 第8节 DSG 驱动程序 本 应用手册中的内容 也可帮助您了解有关 FET 驱动器的更多信息。

此致、

Alexis

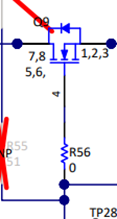

从 BQ76952EVM 中原理图图图图5-11中可以看出、THER 始终是至少一个与 DSG 和 CHG 引脚串联的5.1k 电阻器(不是0r)。 由于我不理解您的反馈、请更详细地解释。

第16.5节仅显示 FET 驱动器的关断、而对导通一无所知。 也没有有效的合成来源。

应用手册"多个 FET"中对不同的开关导通特性进行了测量。 所用/所示的最小值为100R、但不低于该值。 这是限制吗?

如果您可以向我提供额外的反馈、以了解 BQ 在小串联电阻方面的限制以及 DSG 和 CHG 引脚的内部电阻是多少、那会很好。

谢谢

您好、Max:

为困惑道歉。 栅极电阻为0欧姆时指的是 R56、如 EVM 原理图中所示。

应用手册"多个 FET"中提供了不同开关导通特性的测量值。 所用/所示的最小值为100R、但不低于该值。 这是限制吗?

不建议使用低于100欧姆的引脚电阻器来将引脚与电流路径隔离。

此致、

Alexis