工具与软件:

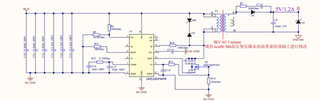

输出5V 1.2A、请帮助检查 原理图 和 PCB、为什么纹波如此高、感谢。μ W

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

尊敬的 Hui、

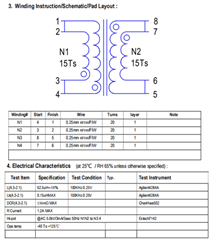

-首先,您能否分享您用于原理图设计的设计计算器工具。 您还能分享一下您的变压器的 DS 吗? 我需要验证 Lmag 和匝数比。

-我建议在 VIN 和 SW 之间添加一个缓冲器来衰减来自开关节点电压的钳位峰值的 HF 谐波。 则可以使用100 Ω+100pF。

- TC:如果您只是在 Ta 环境25°C 下进行测试、则可以将此引脚悬空。 如果在不同的 Ta 下测试、建议在 TC 引脚处使用 TC 电阻器来补偿来自次级二极管的 VF 正向电压变化。

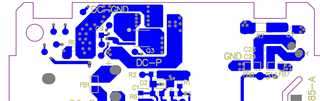

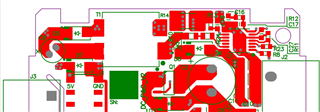

-关于布局:

EN、RSET、SS、COMP 引脚:建议为所有这些引脚的返回路径添加一个信号接地平面、并与更大的 GNDP 平面隔离、并通过 AGND 引脚连接到散热焊盘(最后一个已完成)。 这可改善稳压(COM 引脚的回路)和信号引脚的回路连接。 如果可能、请将这些引脚的所有元件放置在 IC 的一侧、远离开关和电源引脚。 请参阅以下 EVM 布局的示例。

2.将 MOSFET 放置在顶层并放置在变压器旁边。 避免在主开关环路(VIN、XFMR、MOSFET)中使用过孔、因为它们会引入寄生电感、从而产生压降并影响调节。 您可以将 D6和 D8钳位电路放置在底层以获得更大的空间。 请参阅以下 EVM 布局的示例。 这对于尽可能缩短开关环路并改善调节非常重要。

3.在初级侧的所有可用空间上放置一个宽而大的 GNDP 平面。 该接地平面需要连接输入电容器 VIN 的回路和 RC 电阻器的回路(初级开关环路)。 请参阅 EVM 的以下示例。 该接地平面不仅有助于实现良好的热性能、还有助于实现低 EMI、从而减少变压器中漏电感产生的任何残余 H 场。

4.在次级侧的所有可用空间上放置一个宽而大的 GNDS 飞机。 同上。 请参阅 EVM 的以下示例

关于输出纹波、您能否将开关波形与交流输出电压并联? 此外、负载条件是否经过测试、这是在空载还是轻载时? 测试 VIN? 我怀疑 Vout AC 处的这些大 HF 峰值 源于 布局而耦合到 Vout 的 EMI。

谢谢你

随附了我们根据需要提供的计算结果和变压器数据。

此外、我们在测试中发现纹波分为两部分、一部分是开关正常振荡的25kHz 三角波、另一部分是大于1M 的突然电压。

通过调整后端的 MLCC 可以降低突变电压、而通过增加输出的电感和滤波电容可以降低三角波。

因此、我们计划增加输出端2200uF 的滤波电容、同时增加10uF、1uF 和10nF 的高频滤波。

同时、根据以下建议改进电流环路和接地布线。

看看是否有任何其他 suggestions.e2e.ti.com/.../0361.LM5185_2D00_DESIGN_2D00_CALC.xlsx

尊敬的 Hui、

请参阅我的原理图审阅:

-UVLO:为 UVLO_ON 18.8V 和 UVLO_OFF 17.2V 设置了电阻器。 在计算器中、我看到 Vin_Min=9V、低于 UVLO 阈值。 请检查这些值或确认 Vin_min

-FB: 请将 FB 电阻更新为54k Ω。 该值来自反射的 Vout 5V 和 Rset 10k Ω Vref = 1V。

RC 滤波器在 RCS 上:原理图上看不到值。 我建议使用100 Ω+100pF 滤波器。

-mosfet:使用 N 通道、而不是 P 通道。 LM5185的栅极驱动器专为 N 沟道而设计。

-补偿网络, Lmag 和 NPS 看起来不错。

关于波纹,您是否测量输出电压波纹,对吗? 您可以使用 HF 去耦电容(例如 Vout 处的10nF)以及 Lowe 频率滤波电容(例如10uF-1uF)。 我同意使用开关环路、这可以放置接地平面并按照以下建议将其分布在可用空间内。

谢谢你