Other Parts Discussed in Thread: TINA-TI

Thread 中讨论的其他器件:Tina-TI

工具与软件:

尊敬的 E2E 精英:

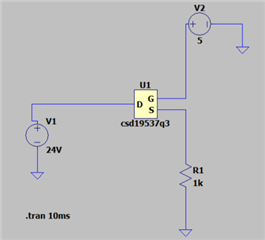

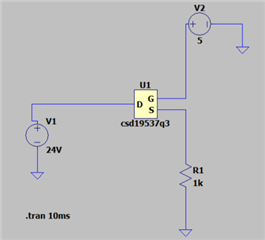

我目前使用从 TI 网站下载的 SPICE 模型、并在 LTSpice 中创建了一个符号。

根据数据表、Vgs 需要典型值3V、以便我的24V 能够降低 R1的电压。

以下是我的仿真结果:

源极侧显示的结果仅为2V、而不是24V。

我有什么不好的地方吗?

谢谢。

此致、

JS.

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

Other Parts Discussed in Thread: TINA-TI

工具与软件:

尊敬的 E2E 精英:

我目前使用从 TI 网站下载的 SPICE 模型、并在 LTSpice 中创建了一个符号。

根据数据表、Vgs 需要典型值3V、以便我的24V 能够降低 R1的电压。

以下是我的仿真结果:

源极侧显示的结果仅为2V、而不是24V。

我有什么不好的地方吗?

谢谢。

此致、

JS.

您好、JS:

感谢您关注 TI FET。 TI 的所有80V 和100V FET 都需要 VGS≥6V、这是在数据表中指定 Rds (on)并在生产中进行测试时的最小值。 TI 不保证 Rds (on)值 VGS 小于6V。 数据表中指定的典型阈值电压 VGS (th)是 FET 刚刚开始导通的位置(ID = 250μA)。 要充分增强 FET、必须将 VGS 驱动至至少6V。 如数据表第1页的 Rds (on)与 VGS 关系图所示、导通电阻图在 VGS = 5V 时几乎为垂直。

仿真将 FET 配置为高侧开关、漏极连接到输入电压、负载/输出电压连接到源极。 在该配置中、栅极电压必须比输入电压至少高6V。 这是因为当 FET 导通时、漏极和源极电压几乎相等。 要使仿真正常工作、栅极电压必须为30V 且 VGS = VG - VS = 30V - 24V = 6V。 您还可以将 V2的基准从 GND 更改为 FET 源、并应用6V、使 VGS = 6V。

尝试在仿真中使用 VGS = 6V (V2 = 30V 以 GND 为基准、或 V2 = 6V 以 FET 的源极为基准)、查看这是否为 FET 的源极提供了预期的输出电压。 当我在 TINA-TI 中复制仿真时、这两个方法都起作用。 我将在下面添加一个链接、以访问关于在使用 FET 进行设计时避免常见错误的应用手册。 如有任何问题、请告诉我。

https://www.ti.com/lit/an/slpa021/slpa021.pdf

此致、

约翰·华莱士

TI FET 应用