Thread 中讨论的其他器件:UCC21732

工具与软件:

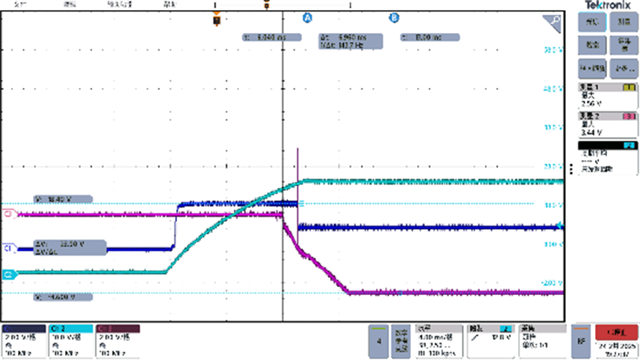

我的 UCC21732始终输出低电平。 图中显示了启动波形、其中 C1是 FLT、C2是 PCB 的24V 电压源(用于生成隔离式 VDD 和 VEE)、而 C3是栅极电压。

电源(包括来自 LDO 的5V VCC、隔离式18V VDD 和来自 UCC14240的-4V VEE)都适用。 RDY 为高电平。 IN+连接到5V、IN-连接到 DGND。 启动后、输出电压被下拉至-4V。

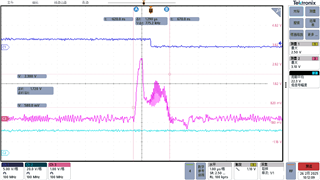

SiCFET (IMW65R039M1HXKSA1)从未开启、因此它无法提供过流保护。 CLMPE-CLMPE VEE 电压为0V、因此我认为外部米勒翻盖电路也不是原因。