工具与软件:

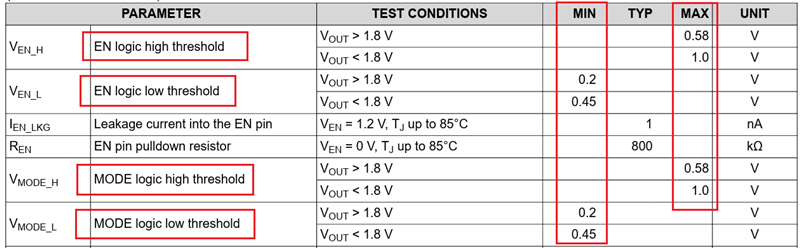

TPS61094的文档说明 EN 逻辑高阈值为:

VOUT > 1.8V = 0.58V (最大值)

VOUT < 1.8V = 1.0V (最大值)

1)我是否正确理解、 高于0.58V 的所有电压都将被视为高电平(对于 Vout > 1.8V 的情况)?

而在 Vout < 1.8V 的情况下、所有 高于1V 的电压都将被视为高电平?

如果我的推理正确、那么我不明白为什么在 Vout 电压较高时、我们会有较低的逻辑高电平阈值?

据我所知、逻辑芯片还有另一个原理:Vout 越高、逻辑高电平阈值就越高。

2) 2) 请说明如何正确理解低逻辑电平阈值?

我是否正确理解低至0.2V 的 电压都被视为低电平(Vout > 1.8V 时)?

而在 Vout < 1.8V 的情况下、低至0.45V 的所有值都被视为低电平?