Other Parts Discussed in Thread: LM5023

主题中讨论的其他器件:LM5023

工具与软件:

感谢您分享上一个主题 SLUAAC5中的有用文章! 其中深入介绍了故障检测机制、我尝试根据建议探测 CS 和 OVP 引脚。 在根据检查数据表对原理图进行一些更新后、我发现 OVP 引脚不再存在问题。

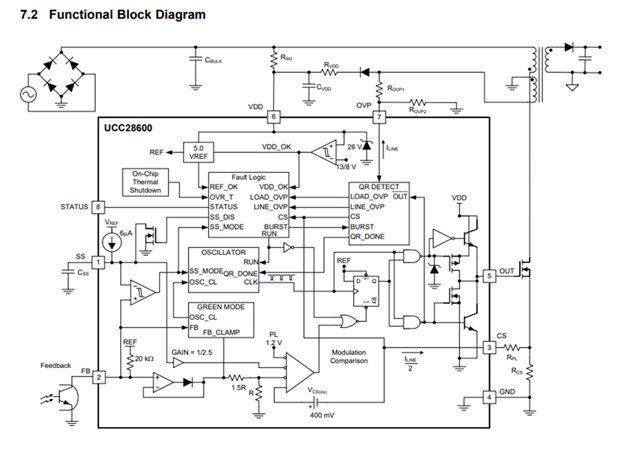

但是、在 RC 和 RPL 值方面仍面临一些挑战。 数据表中似乎有多个计算公式、设计计算器使用不同的方法。 您能否指导我哪种方法更准确或如何更有效地进行这些计算?

我还为不同的输入电压连接了波形。 现在、转换器在120VDC 和180VDC 输入上的运行符合预期、但是初级电流形状仍然不显示为平滑斜坡。 当输入为250VDC 时、即使初级电流在下降时继续增加、输出也不会高于5V。 如随附的波形所示、在325VDC 时、OVP 似乎未触发、这可能与问题相关。

您能否提供有关解决此问题的进一步建议? 此外、如果可能、您是否推荐包含输出 OVP 功能且可在200kHz 以上运行的反激式控制器?

另外、我需要指出的是、LM5023是在之前的文章中提到的、因为我使用的 SPICE 模型经验证是可靠的、因此我认为问题与模型无关。

更新了原理图:https://workdrive.zohopublic.in/file/m492ucd8cc3e83a364cc6b0a90e9bdbc400df

120VDC 输入时的波形:https://workdrive.zohopublic.in/file/m492u5ff8c6947f4b4f50a412d70b7a5273d0

180VDC 输入时的波形:https://workdrive.zohopublic.in/file/m492uaa947a8f9e7844bfb0349eaa147a3f61

250V 直流输入时的波形:https://workdrive.zohopublic.in/file/m492u9774f21ad54041df8cc8c9ecc745ec0a

325VDC 输入端的波形:https://workdrive.zohopublic.in/file/m492uf86440051c0840ed9f9f13935836fcb3

期待您的建议!

此致、