工具与软件:

您好、请使用此主题继续我们的电子邮件和 TI 内部 e2e 论坛讨论。

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

工具与软件:

您好、请使用此主题继续我们的电子邮件和 TI 内部 e2e 论坛讨论。

您好!

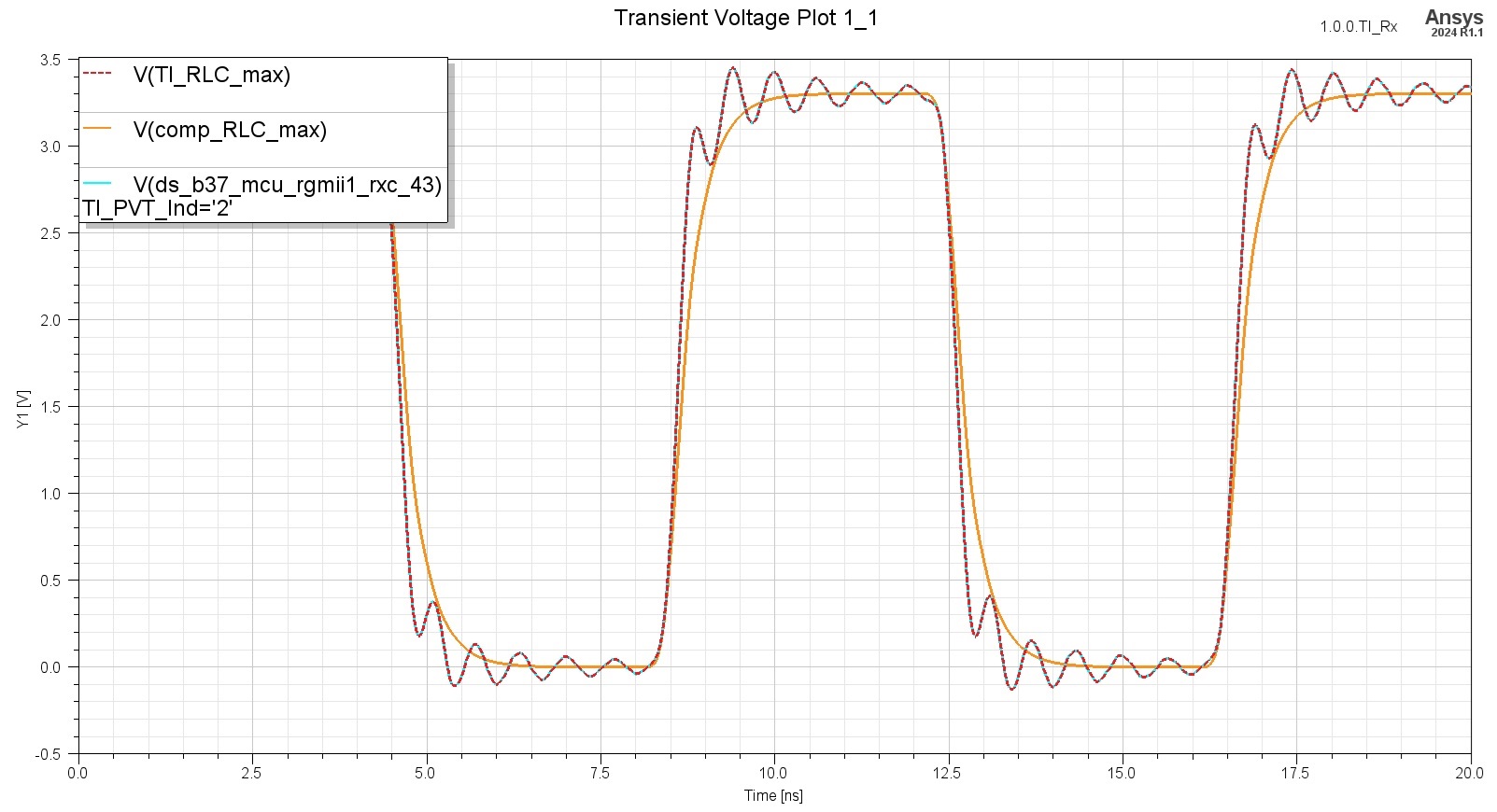

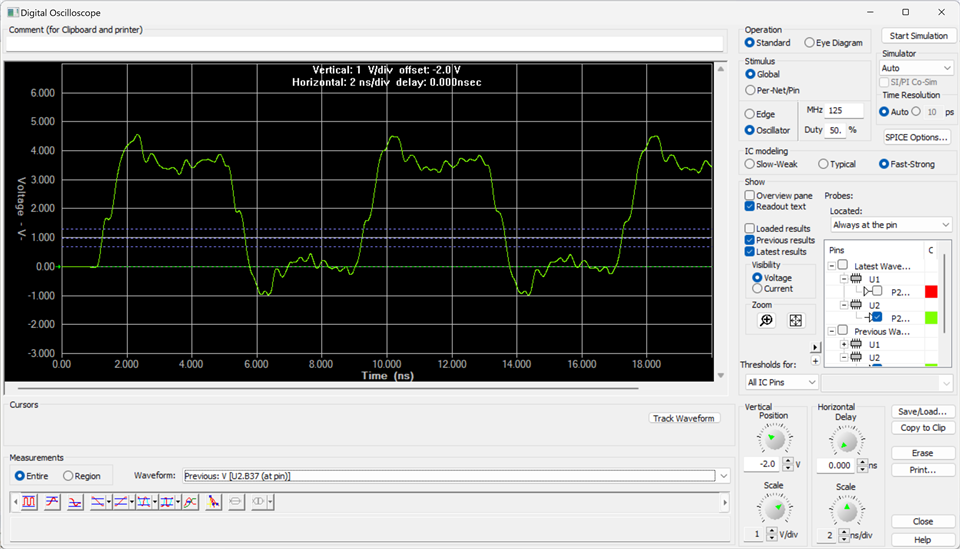

如前所述、在将 TDA 用作 RGMII Rx 时、我会看到有意义的纹波。

这些纹波取决于 PVT 和上升时间。

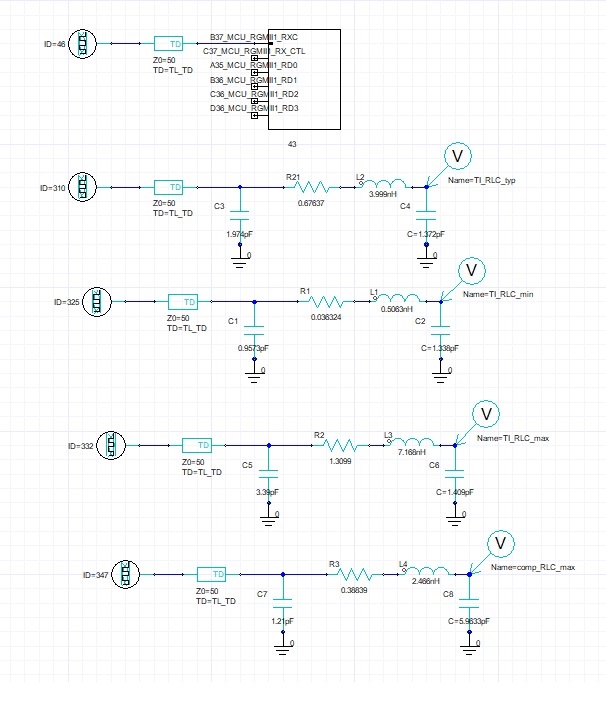

请查看以下的图、其中包含:

PVT 最大值时的 TDA (DS-LVCMOS0_FAST)

2. TX 是一款理想的50欧姆驱动器、TR-0.4ns、clk 模式4ns UI。

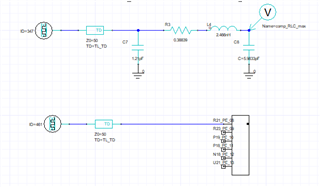

3.调试-与 TDA ibis 文件中的 RLC 电路使用了相同的设置、并与第三方 RGMII Rx RLC 进行了比较。

请参阅下图、了解 PVT 最大值(纹波最强):

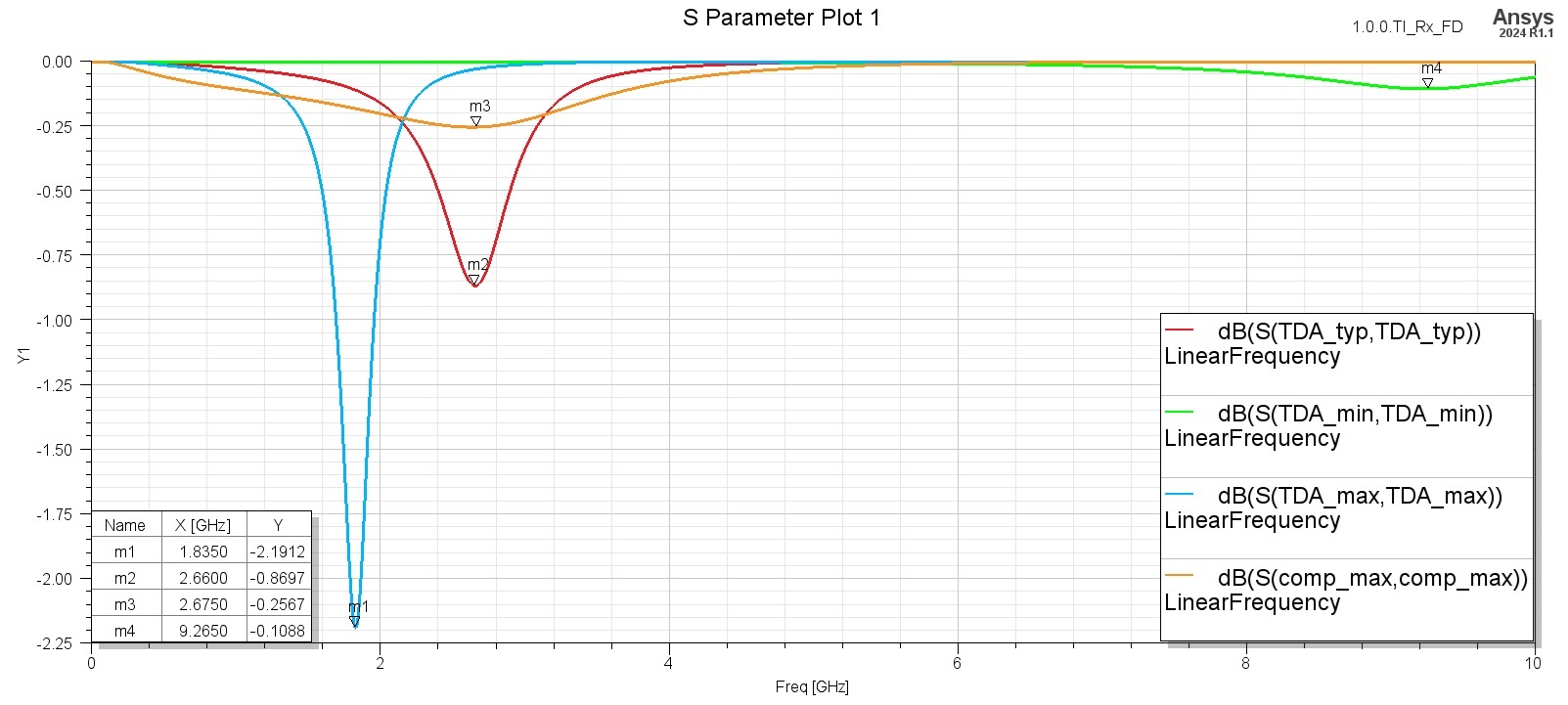

我怀疑根本原因在 RLC 的频域中-请查看下面的回波损耗图:

正在等待回复、

Yoel

尊敬的 Yoel:

您能否尝试此具有更新的 LVCMOS 和 SDIO 缓冲器的 IBIS 模型?

e2e.ti.com/.../j784s4_5F00_v0p2.ibs

此致、

标记

尊敬的 Yoel:

感谢您提供0p1和0p2两种模型的绘图—更新后的 LVCMOS 模型看起来更好。

为了排除任何 IBIS 问题、您能否使用竞争对手的 RLC 值替换我们的 RLC 值、看看问题是否仍然存在?

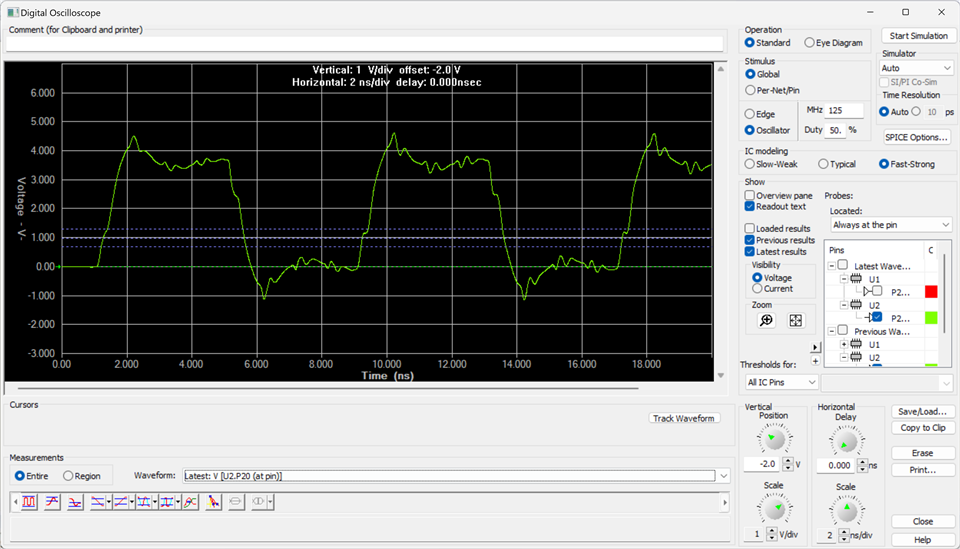

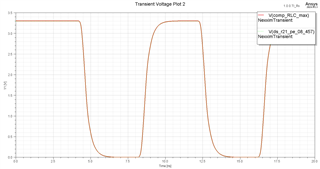

使用 HyperLynx、我使用第三方 TX 对同一第三方 RX 运行了仿真。 结果与 第三方 TX to TI RX 类似。 我们建议与第三方合作、了解通过其 TX 提高信号完整性的选项。

参数:

第三方 TX 与第三方 RX

第三方 TX 到 TI RX

此致、

标记

尊敬的 Mark:

为了澄清、在我发送的所有近期图中、我使用了上升时间为0.4ns 的理想50 Ω 驱动器、而不是第三方 Tx。

以下是第三方 PVT 最大值处的电压图 RLC 与 IBIS 之间的关系、验证不存在 IBIS 建模问题。

关于您发送的图表、不确定具体使用了什么、但看起来您具有几乎4.5V 的峰值电压和-1V 的最小电压 您确定自己的设置了吗? 对于 RGMII 来说不合理,据我所知……

总之、我有一个理想的50欧姆驱动器、我使用 ibis 和 RLC 测试2个不同的接收器。

借助 TI、我可以在典型值和最大 PVT (ibis 和 RLC)下获得强纹波、但第三方没有。

我可以看到 TI RLC 电路在上升时间的 BW 处产生显著谐振、这也导致了纹波。

尊敬的 Yoel:

我与我们的仿真专家交谈、他 建议使用[封装模型]部分而不是[封装]部分的 RLC 值。 [封装模型]部分具有针对给定相关引脚的 RLC 值、而[Package]部分具有针对典型引脚的 RLC 值。

为了方便起见、以下是器件上引脚 B37的 RLC 值(位于[封装模型]部分):

此致、

标记