工具与软件:

您好、TI 专家:

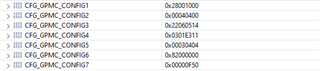

我已开始重新研究这个问题、并尝试转储"CONFIG1 ~ CONFIG7"、请您进行审核。

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

工具与软件:

您好、TI 专家:

我已开始重新研究这个问题、并尝试转储"CONFIG1 ~ CONFIG7"、请您进行审核。

尊敬的 Kallikuppa:

我无法理解您的评论。

您的意思是两次写入之间必须至少有一个时钟周期的延迟? 原因是什么? 另一项信息是我们使用 DMA 在 GPMC 和 SRAM 之间传输数据。

此外、正如本线程所说的、我观察到在两次读取之间没有此类延迟。

您好、Jenny Zhou、

谢谢你。

另外一条信息是我们确实使用 DMA 在 GPMC 和 SRAM 之间传输数据。

我怀疑 DMA 用于读取。

GPMC 写入是导致 CS 切换的 CPU 写入。

此致、

Sreenivasa

您好、Jenny Zhou、

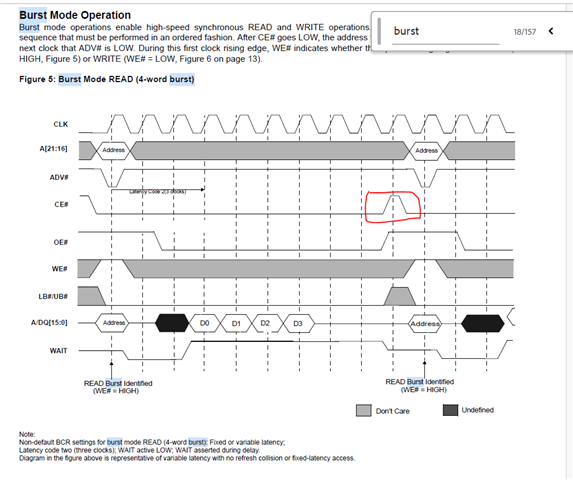

如果你看下面的图片,即使 PSRAM 数据表说,在突发模式下, CS 线路必须更改每个字数据传输在读取和写入周期.

在我看来,你的 观察 是 可以的写入周期和相同的行为应该出现在读取和写入周期.

您能否共享 TX 和 RX 通道的 DMA TR 配置?

前成员、

请在此处确认。

实际上、在用户用例中、它们没有启用突发访问、即使它们没有启用突发模式、为什么 CS 线路在写入周期而不是读取周期中取消置位。

此致、

Anil。