主题中讨论的其他器件:TDA4VM

工具与软件:

您好!

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

尊敬的 Yang:

很高兴见到您回来。

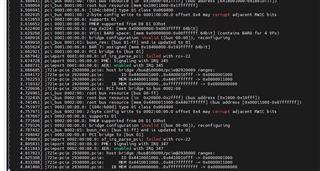

我在共享日志中看到 SERDES 初始化失败、这 也会导致 PCIe 失败、因为 PCIe 依赖于先初始化 SERDES PHY。

我怀疑这是计时问题。 是否有像 TI EVM 上一样提供100MHz 参考时钟的外部时钟发生器? 或者、定制电路板是否没有 SERDES/PCIe 连接器的外部参考时钟?

如果没有外部时钟、则有一个常见问题解答讨论了使用内部参考时钟时发生的变化: https://e2e.ti.com/support/processors-group/processors/f/processors-forum/1004565/faq-tda4vm-tda4vm-dra829v-routing-pcie-reference-clock-externally

此致、

Takuma

您好!

添加 DTS 配置:

e2e.ti.com/.../PCIE_5F00_newdts.txt

此致、

Yang

尊敬的 Yang:

目前、卡滞设备的问题已得到解决、但发现了新问题。

卡住的设备问题是如何解决的? 新日志和旧日志在 SERDES 和 PCIe 方面看起来相同、因此我想知道已实现了哪些更改、以便提供更好的建议。

在任何情况下、我都有几个问题:

至于 DTS、如果使用内部参考时钟、则会发现有问题。 如果使用外部时钟发生器、则会出现其他问题。 如果您能回答以上问题、我可以给出正确的建议。

此致、

Takuma

尊敬的 Yang:

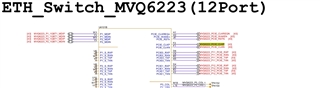

感谢您的原理图。 这种连接方式好像是通过 PCIe 参考时钟从 SoC 直接连接到 PCIe 连接器。 TI EVM 的默认硬件配置是使用外部时钟发生器、因此该硬件差异很可能是导致该问题的原因。

您是否可以尝试添加应影响 PCIe0、1和2的此补丁?

如果这会导致冻结、则可能需要启用时钟。

此致、

Takuma

尊敬的 Yang:

[报价 userid="572765" url="~/support/processors-group/processors/f/processors-forum/1476868/tda4vm-q1-tda4-connects-to-switch-via-pcie/5676971 #5676971"]我看到所有4个 PCIe 的错误、因此我认为不仅 PCIe3有问题。 或者、PCIe3是唯一需要考虑的问题吗、我们可以忽略 PCIe0、1和2?

您是否有可以为我提供的任何补丁程序来尝试解决此问题?

我已在5天前分享了包含补丁的常见问题解答。 我将在此处复制补丁:

我认为它不会完全适用于最新的 SDK、但请参考此补丁来更改最新的 SDK。

此致、

Takuma

您好, 这是添加一个补丁: 0083.0001-PCIe-internal-REFCLK-patches-for-8.6-SDK-on-TDA4VM-J.patch 收集的日志

尊敬的 Yang:

新日志看起来更好、但正如您提到的、日志似乎停止在 PCIe3。

有两点:

出于推理、PCIe 初始化会非常早地停止、因此建议检查复位引脚和时钟问题、因为这些是在 PCIe 内核驱动程序中初始化的一些首要任务。

此致、

Takuma

您好!

尊敬的 Yang:

PCIe 时钟似乎未设置。 我可以在3个工作日内对此进行调查吗?

我怀疑驾驶员被卡在驾驶员的574线附近: https://git.ti.com/cgit/ti-linux-kernel/ti-linux-kernel/tree/drivers/pci/controller/cadence/pci-j721e.c?h=ti-linux-6.6.y#n574

您可以在这里放置一些调试语句、以查看导致问题的确切代码行。

此致、

Takuma

尊敬的 Yang:

在这方面仍然需要一些时间、但想要分享一些发现。

我已经重现了 TI EVM 上的挂起。 TI J721E EVM 没有 PCIe3引脚输出、它用于 USB、但定义 PCIe3仍然应该是可以的、它应该只是错误并继续前进(只是不起作用、因为实际上 EVM 板上没有 PCIe3)。

在8.6 SDK 中看起来像、在 devicetree 中定义 PCIe3不会导致挂起、但在10.1中执行相同的操作会导致挂起。 8.6 SDK 和10.x SDK 之间会发生一个很大的变化、那就是在 U-Boot 中需要进行一些 SERDES 初始化。 我目前怀疑 U-Boot 和 Linux 中的 SERDES 初始化不匹配导致 SERDES3挂起。

此致、

Takuma

尊敬的 Yang:

仍然没有找到"修复"、但在这个问题上取得了一些进展。 我可以多获得2个工作日、以便取得更多进展。

我发现、使用9.2 SDK 中的 U-Boot 和10.1 SDK 中的 Linux 内核、可完全引导至终端、而不会在 PCIe 驱动程序中挂起。 如果您有兴趣、也可以尝试相同的实验、方法是安装9.2 SDK、仅覆盖 U-Boot 二进制文件、同时保留10.1 SDK 中的 Linux 内核。

这使更多人确信问题出在9.x 和10.x SDK 之间的 U-Boot 更改中。 我做了一个实验、从 U-Boot config 中注释掉 Sierra SerDes 和 Wiz 驱动程序、这样它们不会在10.x 中初始化、但在这些更改后问题仍然存在。 我将继续研究该问题、重点关注 U-Boot 的更改、以便查看我们是否可以启动。

此致、

Takuma

您好!

以下是在 U-boot 中关闭串行器/解串器后的 Linux 引导日志:

e2e.ti.com/.../PCIE_5F00_Log.txt

此致、

Yang

尊敬的 Yang:

U-Boot 有两个初始化 Sierra SerDes 的不同位置。 一个位置是 devicetre、另一个位置是由某些 U-Boot 配置控制的特定于电路板的驱动器。 您是否可以尝试应用以下补丁:

e2e.ti.com/.../0001_2D00_remove_2D00_Sierra_2D00_SERDES_2D00_init.patch

此致、

Takuma

您好!

尊敬的 Yang:

除此之外、您还可以做另外两件事:

+&wiz3_pll1_refclk {

+ assigned-clocks = <&wiz3_pll1_refclk>;

+ assigned-clock-parents = <&cmn_refclk1>;

+};

+

+&wiz3_refclk_dig {

+ assigned-clocks = <&wiz3_refclk_dig>;

+ assigned-clock-parents = <&cmn_refclk1>;

+};+&wiz3_pll0_refclk {

+ assigned-clocks = <&wiz3_pll0_refclk>;

+ assigned-clock-parents = <&cmn_refclk1>;

+};

+

+&wiz3_refclk_dig {

+ assigned-clocks = <&wiz3_refclk_dig>;

+ assigned-clock-parents = <&cmn_refclk1>;

+};此致、

Takuma

您好、

您好!

您好、Yang、

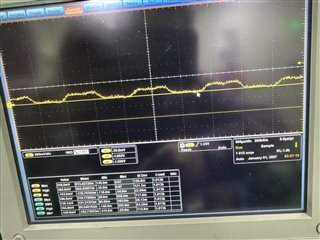

感谢您分享的输出 k3conf 转储时钟295 . 该输出指示 SERDES3 REFCLK 已启用 不是100 MHz 这是 PCIe 需要使用的元件。 外部参考时钟 CMN_refclk1 用作 SERDES3的参考时钟的时钟似乎具有192 MHz 的频率。 请重新检查并告诉我。

或者、 295 4. 和 295 13. 具有所需的100 MHz 频率。 您能否尝试以下差异并检查它是否起作用?

+&wiz3_pll0_refclk {

+ assigned-clocks = <&wiz3_pll0_refclk>;

+ assigned-clock-parents = <&k3_clks 295 13>;

+};

+

+&wiz3_refclk_dig {

+ assigned-clocks = <&wiz3_refclk_dig>;

+ assigned-clock-parents = <&k3_clks 295 13>;

+};您好!

您好、Yang、

请尝试以下差异:

+&wiz3_pll1_refclk {

+ assigned-clocks = <&wiz3_pll1_refclk>;

+ assigned-clock-parents = <&cmn_refclk1>;

+};

+

+&wiz3_refclk_dig {

+ assigned-clocks = <&wiz3_refclk_dig>;

+ assigned-clock-parents = <&cmn_refclk1>;

+};

+&serdes3 {

+ assigned-clocks = <&serdes3 CDNS_SIERRA_PLL_CMNLC>;

+ assigned-clock-parents = <&wiz3_pll1_refclk>;

+};

此致、

Siddharth。

您好!

尊敬的 Yang:

看起来两个日志都没有清理引导、并且 PCIe3正在正确探测。 第二个名为"add_wiz3_REFCLK"的日志似乎在 PCIe3初始化中更进一步,所以它看起来使用 wiz3_pll1_refclk 是正确的。

在第二个日志中、我看到:

[ 5.937282] cdns-sierra-phy 5030000.serdes: Timeout waiting for PHY status ready [ 5.944668] phy phy-5030000.serdes.12: phy poweron failed --> -110 [ 5.950836] j721e-pcie 2930000.pcie: error -ETIMEDOUT: Failed to init phy [ 5.957620] j721e-pcie: probe of 2930000.pcie failed with error -110

您能分享输出吗 k3conf 转储时钟295. 再次使用用于生成 "add_wiz3_refclk" 日志的 devicetree"。

此致、

Takuma

尊敬的 Yang:

我希望我们不要做重复和无用的工作。

对此深表歉意。 您的补丁是正确的。

最新消息是、DEV_SERDES_16G_IP2_LN0/1_TXCLK 均为 CLK_STATE_NOT_READY。 Siddharth 可能有不同的想法、但我们可以再次检查以下寄存器、并添加其他 PCIe 寄存器来进行比较吗?

此致、

Takuma

尊敬的 Yang:

我发现一些有趣的事情可能是导致该问题的根本原因。

目前、使用10.1 SDK U-Boot + Linux 内核、我能够启动 PCIe0、1、2和3控制器(不过、由于 PCIe3没有引脚输出、因此无法测试它是否可以枚举 PCIe 卡)。 下面是我看到的内容:

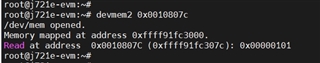

root@j721e-evm:~# lspci 0000:00:00.0 PCI bridge: Texas Instruments Device b00d 0001:00:00.0 PCI bridge: Texas Instruments Device b00d 0002:00:00.0 PCI bridge: Texas Instruments Device b00d 0003:00:00.0 PCI bridge: Texas Instruments Device b00d root@j721e-evm:~# uname -a Linux j721e-evm 6.6.44-ti-gdf658b1b226e-dirty #3 SMP PREEMPT Tue Mar 11 18:25:17 CDT 2025 aarch64 GNU/Linux root@j721e-evm:~#

该更改是对 U-Boot 配置进行了一行更改:

在 Linux 内核中、我进行了以下更改:

e2e.ti.com/.../0001_2D00_adding_2D00_pcie3_2D00_to_2D00_dts.patch

您能否对其进行测试?

此致、

Takuma

尊敬的 Yang:

很高兴听到这个消息!

PCIe 控制器似乎在工作。

使用以太网交换机等实际 PCIe 器件进行测试时、仍需要注意以下两点:

此致、

Takuma