工具与软件:

您好!

我正在使用 TDA4VM、需要配置中断、以便 C66x 无需使用 TI 驱动程序即可通知 R5F、完全采用裸机形式。 我已经检查了 TRM、并确定我需要配置中断控制器和中断路由器(INTRTR)来实现这一点。

但是、我仍然不完全了解寄存器的工作方式或设置它们的正确顺序。 我想知道是否有任何建议 常见问题解答、示例或其他文档 可帮助我更好地理解该流程。

我非常感谢您的任何指导!

此致、

Heverton

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

工具与软件:

您好!

我正在使用 TDA4VM、需要配置中断、以便 C66x 无需使用 TI 驱动程序即可通知 R5F、完全采用裸机形式。 我已经检查了 TRM、并确定我需要配置中断控制器和中断路由器(INTRTR)来实现这一点。

但是、我仍然不完全了解寄存器的工作方式或设置它们的正确顺序。 我想知道是否有任何建议 常见问题解答、示例或其他文档 可帮助我更好地理解该流程。

我非常感谢您的任何指导!

此致、

Heverton

嗨、Heverton:

有关详细信息、请参阅以下常见问题解答:

请随时跟进更多问题

谢谢!

Neehar

Neehar、您好!

首先、感谢您提供这些链接! 他们在了解如何处理中断方面非常有帮助。

我尝试在不使用 OSAL 的情况下配置中断、但即使我按与 OSAL 相同的顺序写入 VIM 寄存器、也没有按预期更新寄存器。

下面是我的当前测试代码:

#include <stdint.h>

#define R5FSS_VIM_BASE 0x0FF80000 // VIM's base address

#define INTR_NUM 0x1 // Interrupt number - group 1

// VIM's registers

#define VIM_RAW (*((volatile uint32_t *)(R5FSS_VIM_BASE + 0x400 + (0x1 * 0x20))))

#define VIM_STS (*((volatile uint32_t *)(R5FSS_VIM_BASE + 0x404 + (0x1 * 0x20))))

#define VIM_INTR_EN_SET (*((volatile uint32_t *)(R5FSS_VIM_BASE + 0x408 + (0x1 * 0x20))))

#define VIM_INTR_EN_CLR (*((volatile uint32_t *)(R5FSS_VIM_BASE + 0x40C + (0x1 * 0x20))))

#define VIM_INTTYPE (*((volatile uint32_t *)(R5FSS_VIM_BASE + 0x41C + (0x1 * 0x20))))

#define VIM_PRI_INT (*((volatile uint32_t *)(R5FSS_VIM_BASE + 0x1000 + (0x1 * 0x4))))

#define VIM_VEC_INT (*((volatile uint32_t *)(R5FSS_VIM_BASE + 0x2000 + (0x1 * 0x4))))

int myISR (void){

// Just a test function

}

int main(void){

uint32_t bit = INTR_NUM;

// Disable the interrupt

VIM_INTR_EN_CLR = (1 << bit);

// Set the interrupt type (0 = level, 1 = pulse)

VIM_INTTYPE |= (1 << bit); // Pulse-triggered

// Set priority (0x0 - 0xF)

VIM_PRI_INT = 0x0;

// Assign the ISR address

VIM_VEC_INT = (uint32_t) myISR;

// Enable the interrupt

VIM_INTR_EN_SET = (1 << bit);

return 0;

}

运行此代码后、我检查 CCS 中的 VIM 寄存器、但它们的值未按预期改变。 即使是诸如启用/禁用中断之类的基本更改也不会反映在寄存器中。

有什么我可能遗漏的东西吗? 是否还需要执行其他步骤来正确写入这些寄存器?

谢谢!

Heverton

Neehar、您好!

我没有测试使用 CSL API 像CSL_vimCfgIntr(),但我能够读取基本的寄存器,如R5FSS_VIM_PID和R5FSS_VIM_INFO,没有任何问题。

我注意到的一点是:我通过观察 CCS 中的寄存器来检查写入是否生效。 最初、更新不符合预期。 然而、当我删除公式(例如0x1 * 0x20)并且只使用具有直接偏移量的基地址时、寄存器开始在 CCS 中正确更新。

这是否意味着具有计算偏移量的寄存器未在 CCS 中正确映射?

谢谢!

Heverton

嗨、Heverton:

我不希望 CCS 中的寄存器地址不正确、但我会仔细检查。

[报价 userid="619458" url="~/support/processors-group/processors/f/processors-forum/1470905/tda4vm-configuring-interrupt-in-c66-and-r5f-baremetal-no-drivers/5655397 #5655397"]然而、当我删除公式(例如0x1 * 0x20)并且只使用具有直接偏移的基地址时、寄存器开始在 CCS 中正确更新。[/QUOT]

即使在删除要计算的公式之后、它是否完全是相同的基址?

谢谢!

Neehar

Neehar、您好!

感谢您的更新、没问题!

在此期间、我有一个简短的问题:

配置 VIM 之后、是否是通过外部源(例如 GPIO 或其他处理器)触发中断(并进入 ISR)的唯一方法? 或者、是否可以手动设置其中一个 VIM 寄存器中的值、以测试它是否正常工作?

另外、我还在努力充分了解中断系统是如何在 TDA4VM 上工作的。 根据我到目前为止收集到的信息、似乎遵循以下流程:

中断源 (例如 GPIO、其他处理器)--> 中断路由器 (特定于每条路由、例如 GPIO 到 R5F)--> 中断控制器 (例如、R5F 上的 VIM)--> 处理器处理中断

这些组件中的每一个都有其各自负责处理中断的寄存器。 例如:

我是否理解正确、或者过程是否不同?

谢谢!

Heverton

嗨、Heverton:

或者是否有办法在其中一个 VIM 寄存器中手动设置一个值来测试它是否正常工作?

您要测试什么? 您是否尝试在 R5F CPU 端进行测试?

您的中断流程主要是正确的、请查看此文档以了解更多信息: https://software-dl.ti.com/jacinto7/esd/processor-sdk-rtos-jacinto7/10_01_00_04/exports/docs/pdk_jacinto_10_01_00_25/docs/trainings/J7_Interrupt_Architecture。pdf

需要注意的一点是、 如果在 MCU R5F 内核或主域 R5F 内核上生成中断、这可能会略有变化。

此外、需要了解的是有多个独立的中断路由器、例如有一个 GPIOMUX_INTRTR0和 R5FSS0_INTRTR0 。

例如、如果将中断路由到 MCU R5F 内核、GPIOMUX_INTRTR0将经过 MAIN2MCU_PLS_INTRTR0、然后到达 MCU_R5FSS0 。 它不会通过 R5FSS0_INTR0。

所有中断在到达 R5F CPU 前通过 VIM、而 R5F CPU 全部是 R5子中断或 R5SS 的一部分。

谢谢!

Neehar

Neehar、您好!

感谢您提供相关文档! 这真的帮我弄清楚了很多事情。

但是、我仍然对中断路由器(IRS)的工作原理感到有点困惑、特别是在其寄存器方面。 由于有多个中断路由器、它们每个都有单独的寄存器、还是它们之间存在共享配置?

为了澄清我现在要做的事情:我正在从连接到 WKUP_GPIO0_4的按钮生成中断、并想将该中断路由到主域中的 R5F。 根据您提供的文档、我的理解是中断流程应该:

WKUP_GPIO0_4 -->中断路由器-->[从 MCU 域到主域]--> R5F (VIM)

是这样吗?

我可以确认按钮能够正确生成中断、但我不确定如何正确配置中断路由器以传递中断。 现在、中断路由器是最让我困惑的部分、尤其是就其接收和转发中断的方式而言。

我使用按钮进行此测试的目的只是为了更好地了解中断在 TDA4VM 上的工作方式。 我的目标是完全掌握中断路由过程、然后再将其应用到更复杂的情况。

非常感谢有关这方面的任何指导!

谢谢!

Heverton

嗨、Heverton:

由于有多个中断路由器、它们是否每个都有单独的寄存器、或者它们之间是否有共享配置?

是的、所有中断路由器都有专门控制该中断路由器的单独寄存器。 它们仅有的寄存器是用于启用或禁用该线路的 PID 和 MUXCNTL 寄存器。

对于将 WKUP_GPIO0_4路由到主域 R5F、流程如下:

WKUP_GPIO0_4 -> WKUP_GPIOMUX_INTRTR -> R5FSS0/1_INTRTR0 -> R5FSS0/1 (VIM -> R5F 内核)

上面的每个段都有自己的配置寄存器。

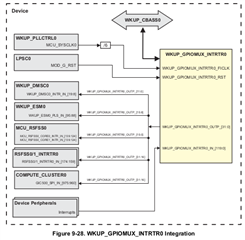

例如、若要将 WKUP_GPIOMUX_INTRTR 路由到 R5FSS0/1_INTRTR0、请查看下面 TRM 中的中断路由器集成:

您必须设置 WKUP_GPIOMUX_INTRTR0_MUXCNTL_n 寄存器才能实现路由。 具体而言、您将选择路由器到 R5FSS0/1_INTRTR0的输出线路之一、例如 WKUP_GPIOMUX_INTR0_OUTP_[31:16](对于 n)。在 WKUP_GPIOMUX_INTR0_MUXCNTL_n 中、您将把位[6:0]设置为外设中断。

在这种情况下、假设您要设置分组中断、您可以将 WKUP_GPIOMUX_INTR0_MUXCNTL_16 [6:0]设置为103、即 WKUP_GPIO0_GPIO_BANK_0。

您是否在使用 TI 提供的驱动程序(例如 Sciclient)? 所有这些都可以在驱动程序内进行处理。

谢谢!

Neehar

Neehar、您好!

我找到了一些有趣的东西。 最新版本的 spruil1c 似乎缺少某些与中断路由器相关的寄存器、例如 GPIOMUX_INTRTR0_INTR_ROUTER_CFG 和 WKUP_GPIOMUX_INTRTR0_CFG 等。 我在以下 TI 论坛帖子中找到了此问题、您还确认缺少 GPIOMUX_INTRTR0_INTR_ROUTER_CFG: e2e.ti.com/.../tda4vm-gpiomux_intrtr0_muxcntl-vanished-from-spruil1b-9-9-9-2-2-to-spruil1c-intended-or-mistake

这就是让我感到困惑的地方。 我是否可以使用替代文档或较旧版本来查找这些缺失的寄存器?

您是否在使用 TI 提供的驱动程序(如 Sciclient)? 所有这些都在驱动程序中处理。

关于这一点、PDK 中的驱动程序是否可以在裸机环境(没有操作系统)中使用? 如果是、是否有任何论坛文章、常见问题解答或文档介绍了如何在 Code Composer Studio (CCS)内的自定义项目中正确使用这些驱动程序?

我曾尝试使用某些驱动程序、但未能使它们正常工作、因此我想我缺少了一些重要的设置步骤。 我特别需要将它们集成到 CCS 中、这是我的主要开发环境。

再次感谢您的帮助!

此致、

Heverton

嗨、Heverton:

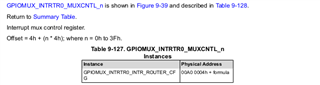

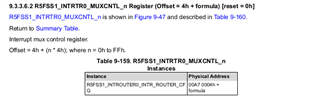

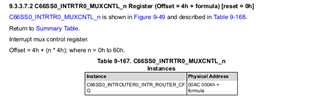

我仍在努力寻找访问这些寄存器的最佳方法。 同时、请告诉我下面有关基地址计算的屏幕截图是否有用:

关于这一点、PDK 中的驱动程序能否在裸机环境(无操作系统)中使用? 如果是、是否有任何论坛文章、常见问题解答或文档介绍了如何在 Code Composer Studio (CCS)内的自定义项目中正确使用这些驱动程序?[/QUOT]您是否在裸机设置(GPIO_LED_Test)中运行了 Baremetal_Led LED 闪烁示例? 如果您在 CCS 中运行此文件 并可以单步执行 、那么您可以 看到如何在裸机环境中使用驱动程序。 此外、该示例还设置 GPIOMUX 和 WKUP_GPIOMUX 路由、因为它可以演示 任何内核的中断。

谢谢!

Neehar

Neehar、您好!

谢谢您的屏幕截图! 它们在阐明 WKUP_GPIOMUX 和 GPIOMUX 中断路由器的基址方面非常有用。

我还有一些关于寄存器字段的其他问题:

此外、我正在尝试确定 R5FSS0_INTRTR0的基址。 我在 MAIN 域存储器映射中发现0x0000A60000对应于 R5FSS0_INTROUTER0_INTR_ROUTER_CFG。 这是 R5FSS0_INTRTR0的正确基地址吗?

再次感谢您的帮助!

此致、

Heverton

嗨、Heverton:

对于所有中断路由器、INT_ENABLE 位是否始终为第16位、或者其位置是否因路由器而异?

正确、所有中断路由器都是相同的。

MUX_CONTROL 位是否始终位于寄存器的下半部分(例如、WKUP_GPIOMUX 中的0-8位)、或者该布局是否因路由器而异?

是的、多路复用器控制始终是低位、但是位数将取决于中断路由器的输出线数。

由于 WKUP_GPIOMUX_INTRTR0有32条输出线(如上面的屏幕截图中 n = 0至1Fh 所示)、多路复用器控制由 WKUP_GPIOMUX_INTRTR0[0:6]表示。

由于 GPIOMUX_INTRTR0有64条输出线路(如上面的屏幕截图中 n = 0至3Fh 所示)、多路复用器控制由 GPIOMUX_INTRTR0[0:8]描述。

这是 R5FSS0_INTRTRTR0的正确基地址吗?

是的、这是正确的地址。

我认为中断路由器寄存器是唯一缺少的寄存器。 我将在下面添加屏幕截图、如果您有任何其他需要、请告诉我:

谢谢!

Neehar

Neehar、您好!

感谢您之前关于中断路由器寄存器的帮助。 我已成功映射所需的地址和配置。

不过、我遇到了尝试向寄存器写入值的问题、但在中进行检查后这些值看起来没有变化 "Memory Browser" 。 Code Composer Studio . 这些值保持在0x0、就像忽略写入一样。

为了测试此行为、我尝试直接写入寄存器、但值不会更新:

volatile uint32_t *test_register = (uint32_t *)(WKUP_GPIOMUX_INTRTR0_BASE + 0x8); *test_register = 10;

void configure_interrupt_routing(){

// Disable the interrupt before configuration (bit 16 = 0)

*wkup_gpiomux_intrtr0_outp_16 &= ~(1 << 16);

*r5fss0_intrtr0_outl_0 &= ~(1 << 16);

// Route WKUP_GPIO0_4 to WKUP_GPIOMUX_INTRTR0_OUTP_16

*wkup_gpiomux_intrtr0_outp_16 = 4;

// Route WKUP_GPIOMUX_INTRTR0_OUTP_16 (input 159 of R5FSS0_INTRTR0) to R5FSS0_INTRTR0_OUTL_0

*r5fss0_intrtr0_outl_0 = 159;

// Re-enable the interrupt (bit 16 = 1)

*wkup_gpiomux_intrtr0_outp_16 |= (1 << 16);

*r5fss0_intrtr0_outl_0 |= (1 << 16);

}

是否有任何特定的保护机制可以阻止对这些寄存器进行写入?

修改任何区域之前是否需要解锁它们?

我感谢有关这一问题的任何指导。

谢谢!

Heverton

嗨、Heverton:

是否有任何特定的保护机制可能阻止对这些寄存器进行写入?

修改任何区域之前、我是否需要解锁它们?

我需要仔细检查是否出现这种情况。

同时、您是否运行了 GPIO Led Blink 示例? GPIO_socConfigIntrPath() API 设置中断路径和中断路由器。 这将是一个很好的开发指南。

谢谢!

Neehar