请注意,本文内容源自机器翻译,可能存在语法或其它翻译错误,仅供参考。如需获取准确内容,请参阅链接中的英语原文或自行翻译。

器件型号:TDA4VH-Q1 工具与软件:

尊敬的社区:

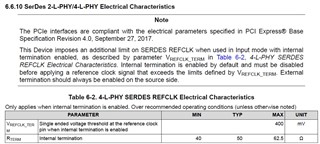

我的问题与 SERDES_REFCLK 输入引脚有关。 数据表中提到了一些我完全不理解的限制

- 据说默认存在内部端接。 我想默认值表示"上电时"。

- 这是正确的吗?

- 如果我们使用 SERDES 进行引导(例如 PCIe)、否则这需要在 SOC 开始执行 ROM 代码之前 SERDES_REFCLK 处于活动状态。

- 这是正确的吗?

- 因此、我们必须遵守表6-2。 问题是我不理解这种情况下"阈值"的含义。

- 这是否意味着 _P 和_N 信号都不应超过400mV? 从而将峰间差分电压限制为很小的量、例如 VoL=0.1V 和 Voh=0.3V

- 这是否意味着_P 必须大于0.4V (同时 N_being < 0.4V)才能被视为"1"?

- 此约束适用于哪个特征尚不清楚。 请您解释一下。

- 该表介绍了内部 RTERM 值。 我想这是指每个_P 和_N 信号看到的负载。

- 这是正确的吗?

- 我知道内部端接可以禁用。

- 如何执行此操作?

此致、

Bruno