工具与软件:

尊敬的 TI 专家:

我们将 GPMC 配置为同步 NOR SRAM 接口以访问我们的 FPGA 的双端口 RAM。

如果我在133M 时钟设置"rdAccessTime = 2"、并且通过将"rdAccessTime=3"或更低的时钟设置为90m 来获得正确的数据、则 GPMC 读取错误的数据。

这是故事。

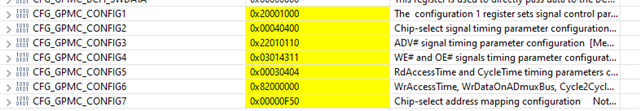

我的时间设置如下:

"…

.timingParams =

{

.csOnTime = 0U、

.csRdOffTime = 4U、

.csWrOffTime = 4U、

.advOnTime = 0U、

.advRdOffTime = 3U、

.advWrOffTime = 3U、

.advAadMuxOnTime = 1U、

.advAadMuxRdOffTime = 2U、

.advAadMuxWROffTime = 2U、

.weOnTtime = 1u、

.weOffTime = 3U、

.oeOnTime = 1u、

.oeOffTime = 3U、

.oeAadMuxOnTime = 1U、

.oeAadMuxOffTime = 2U、

.pageBurstAccess = 0u、

.rdAccessTime = 2U、

.wrAcessTime = 2U、

.rdCycleTime = 4U、

.wrCycleTime = 4U、

.wrDataOnMuxBusTime = 0U、

.cycle2CycleDelay = 0U、

.busTurnAroundTime = 0U、

.cycleDelaySameChipSel = CSL_GPMC_CONFIG6_CYCLE2CYCLESAMECSEN_NOC2CDELAY、

.cycleDelayDiffChipSel = CSL_GPMC_CONFIG6_CYCLE2CYCLEDIFFCSEN_NOC2CDELAY、

}、

…………

从 FPGA 端的捕获快照如下:

正确数据如下

数据错误如下所示

D0和 D1数据正确

我通过 示波器捕获 D0和 D1引脚、这是 GPMC 时钟"15M"和"133M"的结果。 如果"rdAccessTime"为"2"、则 D0和 D1都正确。 无论"15M"或"133M"都是如此。

问题:

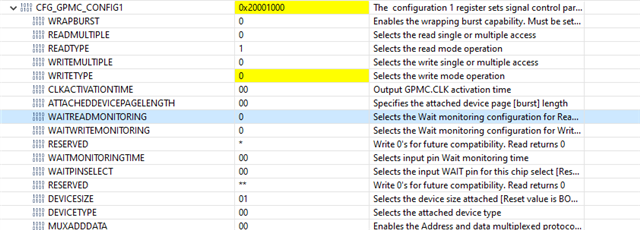

看起来在最大工作频率"133M"时、即使数据物理上正确、GPMC 也无法通过将"rdAccessTime"设置为"2"来正确读取。

因此、对于"133M"、是否存在这样的时间限制(如"rdAccessTime")必须大于2?