主题中讨论的其他器件: TMDS64EVM

工具与软件:

您好!

我们将设计使用 AM6412的电路板、其中外部主电源为3V3。

因此、 VMON_SYS 将来自该电压。

将 VMON_3P3_MCU 和 VMON_3P3_SOC 连接到同一电压轨是否合法?

顺便说一下、数据表图7-5未给出上电序列期间的时序延迟的任何范围。

最低延迟是多少? 最大延迟是多少?

此致、

Bruno

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

工具与软件:

您好!

我们将设计使用 AM6412的电路板、其中外部主电源为3V3。

因此、 VMON_SYS 将来自该电压。

将 VMON_3P3_MCU 和 VMON_3P3_SOC 连接到同一电压轨是否合法?

顺便说一下、数据表图7-5未给出上电序列期间的时序延迟的任何范围。

最低延迟是多少? 最大延迟是多少?

此致、

Bruno

您好 Bruno

感谢您的提问。

VMON_VSYS

这是一个失效防护输入、通过分压器连接。 您可以连接主电压或 SYS 电压进行监控。

该电源可用于早期检测电路板电源故障。

建议通过电阻分压器连接用于生成板载电源的电源/

请参阅 SOC 数据表: 系统电源监测设计指南

3.3V MCU 电源3.135 3.3 3.465V 的 VMON_3P3_MCU 电压监控器

3.3V SoC 电源3.135 3.3 3.465V 的 VMON_3P3_SOC 电压监控器

这些是 SOC 电源监控器、需要连接到任何连接到 IO 组 VDDSHVx 的 SOC IO 电源的 SOC 系统电压

[报价 userid="113256" url="~/support/processors-group/processors/f/processors-forum/1475290/am6412-power-up-timing-delays "]顺便说一下、数据表图7-5未给出上电序列期间的时序延迟的任何范围。

最低延迟是多少? 最大延迟是多少?

[报价]没有最小或最大延迟。

建议在电流电源斜升并保持稳定后斜升下一个电源。

此致、

Sreenivasa

你好、Kallikupa、

感谢您的答复。

1-有一点清楚: VMON VSYS 通过电阻分压器连接到3V3主源。 这不是问题

2 -在我们的板上所有的 VDDSHVxx 将是1V8 :我们不会在所有的3V3接口用于这个应用( VDDA_3P3_SDIO , VDDA_3P3_USB0将连接到 GND ,因为未使用).

因此、我的问题仍然是:是否有可能将 VMON_3P3_MCU 和 VMON_3P3_SOC 连接 到3V3初级电压?

我可以看到的唯一结果是上电序列看起来像图7-5、但具有第一个"导轨"VDDSHV_MCU 、VDDSHV0、VDDSHV1、VDDSHV2、VDDSHV3、VDDSHV4、 VMON_3P3_SOC、VMON_3P3_MCU)在 VMON_VSYS 输入的同时上升(在这种情况下、延时时间= 0)

3 -从图7-5我理解(VDDS_DDR、VDDS_DDR_C)可以在 VDD_CORE 之前或之后建立。

您确认吗?

4 -关于仍不清楚的事情是 MCU_PORz 置为有效之前必须发生的时钟周期数。

这是否可以预制?

此致、

Bruno

Bruno、您好!

与 VDD_CORE 和 VDDR_Cote 相关的问题

[报价 userid="113256" url="~/support/processors-group/processors/f/processors-forum/1475290/am6412-power-up-timing-delays/5663682 #5663682"]3 -从图7-5我理解(VDDS_DDR、VDDS_DDR_C)可以在 VDD_CORE 之前或之后建立。

您确认吗?

[报价]请阅读序列图后的注释

我复制了相关附注:

10、应用于 VDDR_CORE 的电位绝不能大于应用于 VDD_CORE +10的电位。 在上电或断电期间、施加到 VDDR_CORE 的电势绝不能大于施加到 VDD_CORE 的电势+0.18V。 当 VDD_CORE 工作电压为0.75V 时、这要求 VDD_CORE 在 VDDR_CORE 之前斜升并在 VDDR_CORE 之后斜降。 除了为 VDDR_CORE 定义的斜坡要求之外、VDD_CORE 没有任何斜坡要求。 VDD_CORE 和 VDDR_CORE 应由同一电源供电、因此当 VDD_CORE 以0.85V 电压运行时、这些电压会一起斜升。

此致、

Sreenivasa

Bruno、您好!

[报价 userid="113256" url="~/support/processors-group/processors/f/processors-forum/1475290/am6412-power-up-timing-delays/5663682 #5663682"]4 -关于仍不清楚的事情是 MCU_PORz 置为有效之前必须发生的时钟周期数。

这是否可以预制?

[报价]我们以 ms 延时时间来指定它。

请参阅以下内容。

表7-5. MCU_PORz 时序要求

请参阅图7-7

否 参数最小最大值单位

RST1

th (SUPPLYS_VALID - MCU_PORz)

保持时间、上电时 MCU_PORz 有效(低电平)

电源有效后(采用外部晶体电路) 9500000ns

谢谢!

Sreenivasa

Bruno、您好!

[报价 userid="113256" url="~/support/processors-group/processors/f/processors-forum/1475290/am6412-power-up-timing-delays/5663682 #5663682"]-在我们的板上所有的 VDDSHVxx 将是1V8 :我们不会在所有的3V3接口用于这个应用( VDDA_3P3_SDIO , VDDA_3P3_USB0将连接到 GND ,因为未使用).

因此、我的问题仍然是:是否有可能将 VMON_3P3_MCU 和 VMON_3P3_SOC 连接 到3V3初级电压?

[报价]由于存在失效防护问题、因此不建议这样做。

VMON_3P3 MCU 和 SOC 输入可以接地。

我正在与我们的器件专家确认、并将在收到他的消息时进行更新。

此致、

Sreenivasa

Bruno、您好!

感谢您的留言。

[报价 userid="113256" url="~/support/processors-group/processors/f/processors-forum/1475290/am6412-power-up-timing-delays/5663991 #5663991"]您要指出一些关于 VDD_CORE 和 VDDR_CORE 的禁忌、但我的问题是关于 VDDS_DDR (VDDS_DDR_C)相对于 VDD_CORE 的一些禁忌。了解。

[报价 userid="113256" url="~/support/processors-group/processors/f/processors-forum/1475290/am6412-power-up-timing-delays/5663682 #5663682"]3 -从图7-5我理解(VDDS_DDR、VDDS_DDR_C)可以在 VDD_CORE 之前或之后建立。

您确认吗?

[报价]是的。

此致、

Sreenivasa

尊敬的 Kallikupa:

我还有一个关于图7-5的问题

我们可以看到、MCU_OSC0_XI 时钟输入必须为"0"、直到 所有电源稳定、然后才会变为活动状态

但是、当查看 EVM 原理图(TMDS64EVM/ PROC101C (004))、然后进行一些物理测量时、我会看到这种情况不受尊重

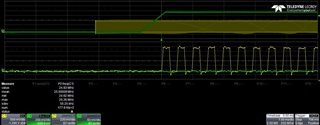

如图所示

: 上屏幕:P0V85 VDDR_CORE 与 MCU 时钟输入混合=> MCU 恰好在 P0V85之前的1.5毫秒内处于活动状态

:下屏幕: MCU_CLOCK 在时钟开始激活的时刻缩放=>时钟测量: 25 MHz : OK

这是否合法?

这是不是可以容忍的?

此致

Bruno

Bruno、您好!

感谢您提供 的意见。

请参阅以下常见问题解答

[报价 userid="113256" url="~/support/processors-group/processors/f/processors-forum/1475290/am6412-power-up-timing-delays/5666771 #5666771"]如图所示

: 上屏幕:P0V85 VDDR_CORE 与 MCU 时钟输入混合=> MCU 恰好在 P0V85之前的1.5毫秒内处于活动状态

:下屏幕: MCU_CLOCK 在时钟开始激活的时刻缩放=>时钟测量: 25 MHz : OK

这是否合法?

这是不是可以容忍的?

[报价]这不是问题。 数据表中的时序图介绍了最坏的情况。

此致、

Sreenivasa

感谢 Kallikupa、

您参考的常见问题解答与 EVM 的情况并不真正匹配、因为在 EVM 中、时钟来自外部源、而不是来自依赖于 VDDS_OSC 的晶体。

在 EVM 中、时钟在所有电源都施加到 MCU 之前很久就开始切换。

关于你的断言: "这不是一个问题。 数据表中的时序图介绍了最坏的情况。 :我是否应该理解,图7-5中显示的几个切换是最小的一个(实际上是1 ,需要2µs ),他们可以开始之前,独立于电源?

您确认吗?

此致、

Bruno

Bruno、您好!

谢谢你。

[报价 userid="113256" url="~/support/processors-group/processors/f/processors-forum/1475290/am6412-power-up-timing-delays/5666939 #5666939"]但你确认:

关于你的断言: "这不是一个问题。 数据表中的时序图介绍了最坏的情况。 :我是否应该理解,图6-5中显示的几个切换是最小的一个(实际上是1 ,需要2µs ),他们可以开始之前,独立于电源?

[报价]在 MCU_PORz 被释放之前、时钟需要保持稳定

MCU_PORz 只有在电源斜升且振荡器稳定后才能释放。

以上理解是正确的。

此致、

Sreenivasa

Bruno、您好!

下面的查询现在是一个单独的线程。

因此我的问题仍然是:是否可以将 VMON_3P3_MCU 和 VMON_3P3_SOC 连接 到3V3初级电压? [报价](+)关于:AM6412:VMON_3P3_MCU 和 VMON_3P3_SOC -处理器论坛-处理器- TI E2E 支持论坛

此致、

Sreenivasa