主题中讨论的其他器件:SysConfig

工具与软件:

在直接模式下、时钟为10M

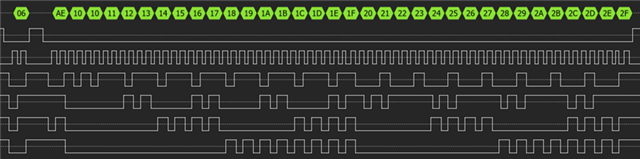

如上图所示调用接口、波形如下所示。

一个帧被分成三个帧。

我想知道这种现象是否正确?

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

您好、Ryan、

对于 NOR 闪存、不能/不支持 OSPI Write Direct。

此致、

Vaibhav

您好、Ryan、

我没有操作或闪存。

好的、我明白了。

写入操作发生在一些内存大小的块中、因此可能就是你看到帧被拆分的原因。

您能否附上一个更详细的说明图表? 我无法理解什么是时钟/数据线路/芯片选择线路。

此致、

Vaibhav

您好、Ryan、

、数量为0x40

在这里、"数量"一词具体是什么意思?

此致、

Vaibhav

您好、Ryan、

这只是为了确认。

写入操作从地址0x00开始、数量为0x40。

这就像整个帧从地址0x0开始并传输64个字节一样?

第三个帧从地址0x30开始、数量为0x10。

最后一帧从地址0x30开始并发送16个字节的数据?

您能详细介绍一下这里的地址是什么吗?

当您说整个帧从地址0x0开始时、这是否意味着您正在写入 偏移为0x0的闪存?

请澄清我的理解。

此致、

Vaibhav

您好、Ryan、

是的、地址是指偏移量。

好的、我明白了。

我将查看您所附加的示意图、我假设您仅启动了一次传输写入、地址/闪存偏移量为0x0、大小为64字节、但是随后您看到发送了3个帧、而不是仅发送了一个由64字节组成的大帧。

此外、您的 SBL 空/引导加载程序映像是否在闪存中的偏移0x0处刷写? 如果是这种情况、建议不要将任何值写入0x0 offset、因为它会覆盖您的 SBL Null 已刷写映像。

此致、

Vaibhav

您好!

除此之外、您还可以提醒我您正在使用的 SDK 版本、以便我可以继续检查 WRITE Direct API 实现。

由于尚未发布,我将查看最新版本,并将在一天内提供有关 Flash_WRITE() API 实现的更新。

此致、

Vaibhav

您好、Vicent:

请参阅 spriuim2h.pdf 中的第12.3.2.5.4章"工作旧模式的接口支持"。 对于 TX-FIFO 和 RX-FIFO 的有限深度、将使用寄存器 OSPI_TX_THRESH_REG 和 OSPI_RX_THRESH_REG、最大大小为32字节。 转储两个寄存器、以检查阈值是否合理。 如果事务长度大于 FIFO 深度、帧会相应地分开。

Linjun

将回复移动到此主题帖、然后关闭另一个主题帖。

您好!

OSPI 性能可在以下位置找到: https://software-dl.ti.com/mcu-plus-sdk/esd/AM64X/10_01_00_32/exports/docs/api_guide_am64x/DATASHEET_AM243X_EVM.html#autotoc_md491

另外、您还可以说明用于通信的 FPGA 的存储器类型吗? 是 NOR 还是 NAND?

此致、

Vaibhav

尊敬的 Vaibhav:

客户捕获以下波形以读取 NOR 闪存(W25Q256JVFQ 128字节。 我们可以看到、低级 OSPI 控制器通过两个事务读取这128个字节、第一个帧从0x0读取到0x53、第二个事务从0x40读取到0x7F、

问题是为什么发生重叠数据事务? 并且没有常规帧大小、低级 OPSI 控制器的行为是什么? 请直接回复此问题、或向 OSPI 控制器 IP 所有者寻求帮助。 谢谢。

此致、

Linjun

您好!

请直接回复此问题或求助于 OSPI 控制器 IP 所有者。

我会包括相关工程师。

期待您的答复。

此致、

Vaibhav

您好!

1. 使用的接口是 OSPI_readDirect API。

2. 配置如下:

/** * Write custom configuration values to the imported modules. */ flash1.$name = "CONFIG_FLASH0"; flash1.device = "CUSTOM_FLASH"; flash1.skipHwInit = true; flash1.fname = "W25Q256"; flash1.protocol = "1s_1s_4s"; flash1.flashSize = 33554432; flash1.flashManfId = "0xEF"; flash1.flashBlockSize = 65536; flash1.cmdBlockErase3B = "0xD8"; flash1.cmdBlockErase4B = "0xD8"; flash1.cmdSectorErase3B = "0x20"; flash1.cmdSectorErase4B = "0x20"; flash1.cmdRd = "0x6C"; flash1.cmdWr = "0x32"; flash1.dummyClksCmd = 0; flash1.dummyClksRd = 8; flash1.flashQeType = "4"; flash1.proto_isAddrReg = false; flash1.dummy_isAddrReg = false; flash1.strDtr_isAddrReg = false; flash1.resetType = "0x30"; flash1.cmdExtType = "NONE"; flash1.xspiWipRdCmd = "0x00"; flash1.xspiWipReg = "0x00000000"; flash1.idNumBytes = 5; flash1.dummyId8 = 0; flash1.fourByteEnableSeq = "0xA5"; flash1.flashDeviceBusyTimeout = 80000000; flash1.flashPageProgTimeout = 704; flash1.flashDeviceId = "0x7019"; flash1.peripheralDriver.$name = "CONFIG_OSPI0"; flash1.peripheralDriver.inputClkFreq = 200000000; flash1.peripheralDriver.dmaEnable = true; flash1.peripheralDriver.baudRateDiv = 20; flash1.peripheralDriver.OSPI.CLK.rx = true; flash1.peripheralDriver.OSPI.DQS.$used = false; flash1.peripheralDriver.OSPI.D7.rx = false; flash1.peripheralDriver.OSPI.D7.$used = false; flash1.peripheralDriver.OSPI.D6.rx = false; flash1.peripheralDriver.OSPI.D6.$used = false; flash1.peripheralDriver.OSPI.D5.rx = false; flash1.peripheralDriver.OSPI.D5.$used = false; flash1.peripheralDriver.OSPI.D4.rx = false; flash1.peripheralDriver.OSPI.D4.$used = false;

BR

Ryan

您好、Ryan、

当您发送某些字节或接收一些字节时、应该寻找帧分离/重叠的方法、因为这不应该发生。

原因:

对于 WRITE DIRECT 和 READ DIRECT API、低级别的实现只是一个简单的 memcopy 操作、根据您最后的响应、通过 memcopy 读取128字节应该是单个事务、不会重叠。

我已增加了这一问题的优先次序、以扩大能见度、并将在我们取得进展时作出同样的回应。

此致、

Vaibhav

您好、Ryan、

您能否使用附加的脚本转储 OSPI 寄存器并在此处共享? 谢谢。

/cfs-file/__key/communityserver-discussions-components-files/791/1462.AM64_5F00_OSPI.tar.xz

Linjun

尊敬的 Linjun:

寄存器值如下所示:

CortexA53_0: GEL Output: OSPI0__OSPI_CFG_VBUSP__VBP2APB_WRAP__OSPI_CFG_VBP__OSPI_FLASH_APB_REGS_config_reg:Reg_0x0FC40000 : 0x80483841 CortexA53_0: GEL Output: OSPI0__OSPI_CFG_VBUSP__VBP2APB_WRAP__OSPI_CFG_VBP__OSPI_FLASH_APB_REGS_dev_instr_rd_config_reg:Reg_0x0FC40004 : 0x0802006C CortexA53_0: GEL Output: OSPI0__OSPI_CFG_VBUSP__VBP2APB_WRAP__OSPI_CFG_VBP__OSPI_FLASH_APB_REGS_dev_instr_wr_config_reg:Reg_0x0FC40008 : 0x00020032 CortexA53_0: GEL Output: OSPI0__OSPI_CFG_VBUSP__VBP2APB_WRAP__OSPI_CFG_VBP__OSPI_FLASH_APB_REGS_dev_delay_reg:Reg_0x0FC4000C : 0x0A0A0A0A CortexA53_0: GEL Output: OSPI0__OSPI_CFG_VBUSP__VBP2APB_WRAP__OSPI_CFG_VBP__OSPI_FLASH_APB_REGS_rd_data_capture_reg:Reg_0x0FC40010 : 0x00000029 CortexA53_0: GEL Output: OSPI0__OSPI_CFG_VBUSP__VBP2APB_WRAP__OSPI_CFG_VBP__OSPI_FLASH_APB_REGS_dev_size_config_reg:Reg_0x0FC40014 : 0x00101003 CortexA53_0: GEL Output: OSPI0__OSPI_CFG_VBUSP__VBP2APB_WRAP__OSPI_CFG_VBP__OSPI_FLASH_APB_REGS_sram_partition_cfg_reg:Reg_0x0FC40018 : 0x0000003F CortexA53_0: GEL Output: OSPI0__OSPI_CFG_VBUSP__VBP2APB_WRAP__OSPI_CFG_VBP__OSPI_FLASH_APB_REGS_ind_AHB_addr_trigger_reg:Reg_0x0FC4001C : 0x00000000 CortexA53_0: GEL Output: OSPI0__OSPI_CFG_VBUSP__VBP2APB_WRAP__OSPI_CFG_VBP__OSPI_FLASH_APB_REGS_dma_periph_config_reg:Reg_0x0FC40020 : 0x00000000 CortexA53_0: GEL Output: OSPI0__OSPI_CFG_VBUSP__VBP2APB_WRAP__OSPI_CFG_VBP__OSPI_FLASH_APB_REGS_remap_addr_reg:Reg_0x0FC40024 : 0x00000000 CortexA53_0: GEL Output: OSPI0__OSPI_CFG_VBUSP__VBP2APB_WRAP__OSPI_CFG_VBP__OSPI_FLASH_APB_REGS_mode_bit_config_reg:Reg_0x0FC40028 : 0x00000000 CortexA53_0: GEL Output: OSPI0__OSPI_CFG_VBUSP__VBP2APB_WRAP__OSPI_CFG_VBP__OSPI_FLASH_APB_REGS_sram_fill_reg:Reg_0x0FC4002C : 0x00000000 CortexA53_0: GEL Output: OSPI0__OSPI_CFG_VBUSP__VBP2APB_WRAP__OSPI_CFG_VBP__OSPI_FLASH_APB_REGS_tx_thresh_reg:Reg_0x0FC40030 : 0x00000001 CortexA53_0: GEL Output: OSPI0__OSPI_CFG_VBUSP__VBP2APB_WRAP__OSPI_CFG_VBP__OSPI_FLASH_APB_REGS_rx_thresh_reg:Reg_0x0FC40034 : 0x00000001 CortexA53_0: GEL Output: OSPI0__OSPI_CFG_VBUSP__VBP2APB_WRAP__OSPI_CFG_VBP__OSPI_FLASH_APB_REGS_write_completion_ctrl_reg:Reg_0x0FC40038 : 0x000340FF CortexA53_0: GEL Output: OSPI0__OSPI_CFG_VBUSP__VBP2APB_WRAP__OSPI_CFG_VBP__OSPI_FLASH_APB_REGS_no_of_polls_bef_exp_reg:Reg_0x0FC4003C : 0xFFFFFFFF CortexA53_0: GEL Output: OSPI0__OSPI_CFG_VBUSP__VBP2APB_WRAP__OSPI_CFG_VBP__OSPI_FLASH_APB_REGS_irq_status_reg:Reg_0x0FC40040 : 0x00000000 CortexA53_0: GEL Output: OSPI0__OSPI_CFG_VBUSP__VBP2APB_WRAP__OSPI_CFG_VBP__OSPI_FLASH_APB_REGS_irq_mask_reg:Reg_0x0FC40044 : 0x00000000 CortexA53_0: GEL Output: OSPI0__OSPI_CFG_VBUSP__VBP2APB_WRAP__OSPI_CFG_VBP__OSPI_FLASH_APB_REGS_lower_wr_prot_reg:Reg_0x0FC40050 : 0x00000000 CortexA53_0: GEL Output: OSPI0__OSPI_CFG_VBUSP__VBP2APB_WRAP__OSPI_CFG_VBP__OSPI_FLASH_APB_REGS_upper_wr_prot_reg:Reg_0x0FC40054 : 0x00000000 CortexA53_0: GEL Output: OSPI0__OSPI_CFG_VBUSP__VBP2APB_WRAP__OSPI_CFG_VBP__OSPI_FLASH_APB_REGS_wr_prot_ctrl_reg:Reg_0x0FC40058 : 0x00000000 CortexA53_0: GEL Output: OSPI0__OSPI_CFG_VBUSP__VBP2APB_WRAP__OSPI_CFG_VBP__OSPI_FLASH_APB_REGS_indirect_read_xfer_watermark_reg:Reg_0x0FC40064 : 0x00000000 CortexA53_0: GEL Output: OSPI0__OSPI_CFG_VBUSP__VBP2APB_WRAP__OSPI_CFG_VBP__OSPI_FLASH_APB_REGS_indirect_read_xfer_start_reg:Reg_0x0FC40068 : 0x00000000 CortexA53_0: GEL Output: OSPI0__OSPI_CFG_VBUSP__VBP2APB_WRAP__OSPI_CFG_VBP__OSPI_FLASH_APB_REGS_indirect_read_xfer_num_bytes_reg:Reg_0x0FC4006C : 0x00000000 CortexA53_0: GEL Output: OSPI0__OSPI_CFG_VBUSP__VBP2APB_WRAP__OSPI_CFG_VBP__OSPI_FLASH_APB_REGS_indirect_write_xfer_watermark_reg:Reg_0x0FC40074 : 0xFFFFFFFF CortexA53_0: GEL Output: OSPI0__OSPI_CFG_VBUSP__VBP2APB_WRAP__OSPI_CFG_VBP__OSPI_FLASH_APB_REGS_indirect_write_xfer_start_reg:Reg_0x0FC40078 : 0x00000000 CortexA53_0: GEL Output: OSPI0__OSPI_CFG_VBUSP__VBP2APB_WRAP__OSPI_CFG_VBP__OSPI_FLASH_APB_REGS_indirect_write_xfer_num_bytes_reg:Reg_0x0FC4007C : 0x00000000 CortexA53_0: GEL Output: OSPI0__OSPI_CFG_VBUSP__VBP2APB_WRAP__OSPI_CFG_VBP__OSPI_FLASH_APB_REGS_indirect_trigger_addr_range_reg:Reg_0x0FC40080 : 0x00000004 CortexA53_0: GEL Output: OSPI0__OSPI_CFG_VBUSP__VBP2APB_WRAP__OSPI_CFG_VBP__OSPI_FLASH_APB_REGS_flash_cmd_addr_reg:Reg_0x0FC40094 : 0x00800004 CortexA53_0: GEL Output: OSPI0__OSPI_CFG_VBUSP__VBP2APB_WRAP__OSPI_CFG_VBP__OSPI_FLASH_APB_REGS_flash_rd_data_lower_reg:Reg_0x0FC400A0 : 0x00000021 CortexA53_0: GEL Output: OSPI0__OSPI_CFG_VBUSP__VBP2APB_WRAP__OSPI_CFG_VBP__OSPI_FLASH_APB_REGS_flash_rd_data_upper_reg:Reg_0x0FC400A4 : 0x00000000 CortexA53_0: GEL Output: OSPI0__OSPI_CFG_VBUSP__VBP2APB_WRAP__OSPI_CFG_VBP__OSPI_FLASH_APB_REGS_flash_wr_data_lower_reg:Reg_0x0FC400A8 : 0x00000020 CortexA53_0: GEL Output: OSPI0__OSPI_CFG_VBUSP__VBP2APB_WRAP__OSPI_CFG_VBP__OSPI_FLASH_APB_REGS_flash_wr_data_upper_reg:Reg_0x0FC400AC : 0x00000000 CortexA53_0: GEL Output: OSPI0__OSPI_CFG_VBUSP__VBP2APB_WRAP__OSPI_CFG_VBP__OSPI_FLASH_APB_REGS_polling_flash_status_reg:Reg_0x0FC400B0 : 0x00000000 CortexA53_0: GEL Output: OSPI0__OSPI_CFG_VBUSP__VBP2APB_WRAP__OSPI_CFG_VBP__OSPI_FLASH_APB_REGS_phy_master_control_reg:Reg_0x0FC400B8 : 0x00800000 CortexA53_0: GEL Output: OSPI0__OSPI_CFG_VBUSP__VBP2APB_WRAP__OSPI_CFG_VBP__OSPI_FLASH_APB_REGS_dll_observable_lower_reg:Reg_0x0FC400BC : 0x00FF81F9 CortexA53_0: GEL Output: OSPI0__OSPI_CFG_VBUSP__VBP2APB_WRAP__OSPI_CFG_VBP__OSPI_FLASH_APB_REGS_dll_observable_upper_reg:Reg_0x0FC400C0 : 0x00000000 CortexA53_0: GEL Output: OSPI0__OSPI_CFG_VBUSP__VBP2APB_WRAP__OSPI_CFG_VBP__OSPI_FLASH_APB_REGS_opcode_ext_lower_reg:Reg_0x0FC400E0 : 0x0302FA00 CortexA53_0: GEL Output: OSPI0__OSPI_CFG_VBUSP__VBP2APB_WRAP__OSPI_CFG_VBP__OSPI_FLASH_APB_REGS_opcode_ext_upper_reg:Reg_0x0FC400E4 : 0x06F90000 CortexA53_0: GEL Output: OSPI0__OSPI_CFG_VBUSP__VBP2APB_WRAP__OSPI_CFG_VBP__OSPI_FLASH_APB_REGS_module_id_reg:Reg_0x0FC400FC : 0x03000300 CortexA53_0: GEL Output: OSPI0__OSPI_CFG_VBUSP__MMR__MMRVBP__REGS_PID:Reg_0x0FC44000 : 0x68747900 CortexA53_0: GEL Output: OSPI0__OSPI_CFG_VBUSP__MMR__MMRVBP__REGS_CTRL:Reg_0x0FC44004 : 0x00000000 CortexA53_0: GEL Output: OSPI0__OSPI_CFG_VBUSP__MMR__MMRVBP__REGS_STAT:Reg_0x0FC44008 : 0x00000002

BR

Ryan

Ryan、您好!

向您提问:

闪存配置值配置不正确。

我查看了数据表、结果发现以下值不正确、我在中添加了注释 红色

关于我的行动项目:

我将在某个时间内探测数据线、并检查是否存在意外的重叠行为。

此致、

Vaibhav

各位专家、您好!

为了重点介绍目标、这里是总结。

我们遇到的问题:

我们需要的支持:

如有任何问题、请告诉我。

尊敬的 Linjun:

1、 间接模式下的读操作被拆分为多个请求。

寄存器值如下所示:

CortexA53_0: GEL Output: OSPI0__OSPI_CFG_VBUSP__VBP2APB_WRAP__OSPI_CFG_VBP__OSPI_FLASH_APB_REGS_config_reg:Reg_0x0FC40000 : 0x80083841 CortexA53_0: GEL Output: OSPI0__OSPI_CFG_VBUSP__VBP2APB_WRAP__OSPI_CFG_VBP__OSPI_FLASH_APB_REGS_dev_instr_rd_config_reg:Reg_0x0FC40004 : 0x0802006C CortexA53_0: GEL Output: OSPI0__OSPI_CFG_VBUSP__VBP2APB_WRAP__OSPI_CFG_VBP__OSPI_FLASH_APB_REGS_dev_instr_wr_config_reg:Reg_0x0FC40008 : 0x00020032 CortexA53_0: GEL Output: OSPI0__OSPI_CFG_VBUSP__VBP2APB_WRAP__OSPI_CFG_VBP__OSPI_FLASH_APB_REGS_dev_delay_reg:Reg_0x0FC4000C : 0x0A0A0A0A CortexA53_0: GEL Output: OSPI0__OSPI_CFG_VBUSP__VBP2APB_WRAP__OSPI_CFG_VBP__OSPI_FLASH_APB_REGS_rd_data_capture_reg:Reg_0x0FC40010 : 0x00000029 CortexA53_0: GEL Output: OSPI0__OSPI_CFG_VBUSP__VBP2APB_WRAP__OSPI_CFG_VBP__OSPI_FLASH_APB_REGS_dev_size_config_reg:Reg_0x0FC40014 : 0x00101003 CortexA53_0: GEL Output: OSPI0__OSPI_CFG_VBUSP__VBP2APB_WRAP__OSPI_CFG_VBP__OSPI_FLASH_APB_REGS_sram_partition_cfg_reg:Reg_0x0FC40018 : 0x0000003F CortexA53_0: GEL Output: OSPI0__OSPI_CFG_VBUSP__VBP2APB_WRAP__OSPI_CFG_VBP__OSPI_FLASH_APB_REGS_ind_AHB_addr_trigger_reg:Reg_0x0FC4001C : 0x00000000 CortexA53_0: GEL Output: OSPI0__OSPI_CFG_VBUSP__VBP2APB_WRAP__OSPI_CFG_VBP__OSPI_FLASH_APB_REGS_dma_periph_config_reg:Reg_0x0FC40020 : 0x00000000 CortexA53_0: GEL Output: OSPI0__OSPI_CFG_VBUSP__VBP2APB_WRAP__OSPI_CFG_VBP__OSPI_FLASH_APB_REGS_remap_addr_reg:Reg_0x0FC40024 : 0x00000000 CortexA53_0: GEL Output: OSPI0__OSPI_CFG_VBUSP__VBP2APB_WRAP__OSPI_CFG_VBP__OSPI_FLASH_APB_REGS_mode_bit_config_reg:Reg_0x0FC40028 : 0x00000000 CortexA53_0: GEL Output: OSPI0__OSPI_CFG_VBUSP__VBP2APB_WRAP__OSPI_CFG_VBP__OSPI_FLASH_APB_REGS_sram_fill_reg:Reg_0x0FC4002C : 0x00000000 CortexA53_0: GEL Output: OSPI0__OSPI_CFG_VBUSP__VBP2APB_WRAP__OSPI_CFG_VBP__OSPI_FLASH_APB_REGS_tx_thresh_reg:Reg_0x0FC40030 : 0x00000001 CortexA53_0: GEL Output: OSPI0__OSPI_CFG_VBUSP__VBP2APB_WRAP__OSPI_CFG_VBP__OSPI_FLASH_APB_REGS_rx_thresh_reg:Reg_0x0FC40034 : 0x00000001 CortexA53_0: GEL Output: OSPI0__OSPI_CFG_VBUSP__VBP2APB_WRAP__OSPI_CFG_VBP__OSPI_FLASH_APB_REGS_write_completion_ctrl_reg:Reg_0x0FC40038 : 0x000340FF CortexA53_0: GEL Output: OSPI0__OSPI_CFG_VBUSP__VBP2APB_WRAP__OSPI_CFG_VBP__OSPI_FLASH_APB_REGS_no_of_polls_bef_exp_reg:Reg_0x0FC4003C : 0xFFFFFFFF CortexA53_0: GEL Output: OSPI0__OSPI_CFG_VBUSP__VBP2APB_WRAP__OSPI_CFG_VBP__OSPI_FLASH_APB_REGS_irq_status_reg:Reg_0x0FC40040 : 0x00000000 CortexA53_0: GEL Output: OSPI0__OSPI_CFG_VBUSP__VBP2APB_WRAP__OSPI_CFG_VBP__OSPI_FLASH_APB_REGS_irq_mask_reg:Reg_0x0FC40044 : 0x00000000 CortexA53_0: GEL Output: OSPI0__OSPI_CFG_VBUSP__VBP2APB_WRAP__OSPI_CFG_VBP__OSPI_FLASH_APB_REGS_lower_wr_prot_reg:Reg_0x0FC40050 : 0x00000000 CortexA53_0: GEL Output: OSPI0__OSPI_CFG_VBUSP__VBP2APB_WRAP__OSPI_CFG_VBP__OSPI_FLASH_APB_REGS_upper_wr_prot_reg:Reg_0x0FC40054 : 0x00000000 CortexA53_0: GEL Output: OSPI0__OSPI_CFG_VBUSP__VBP2APB_WRAP__OSPI_CFG_VBP__OSPI_FLASH_APB_REGS_wr_prot_ctrl_reg:Reg_0x0FC40058 : 0x00000000 CortexA53_0: GEL Output: OSPI0__OSPI_CFG_VBUSP__VBP2APB_WRAP__OSPI_CFG_VBP__OSPI_FLASH_APB_REGS_indirect_read_xfer_watermark_reg:Reg_0x0FC40064 : 0x00000010 CortexA53_0: GEL Output: OSPI0__OSPI_CFG_VBUSP__VBP2APB_WRAP__OSPI_CFG_VBP__OSPI_FLASH_APB_REGS_indirect_read_xfer_start_reg:Reg_0x0FC40068 : 0x01000000 CortexA53_0: GEL Output: OSPI0__OSPI_CFG_VBUSP__VBP2APB_WRAP__OSPI_CFG_VBP__OSPI_FLASH_APB_REGS_indirect_read_xfer_num_bytes_reg:Reg_0x0FC4006C : 0x00000080 CortexA53_0: GEL Output: OSPI0__OSPI_CFG_VBUSP__VBP2APB_WRAP__OSPI_CFG_VBP__OSPI_FLASH_APB_REGS_indirect_write_xfer_watermark_reg:Reg_0x0FC40074 : 0xFFFFFFFF CortexA53_0: GEL Output: OSPI0__OSPI_CFG_VBUSP__VBP2APB_WRAP__OSPI_CFG_VBP__OSPI_FLASH_APB_REGS_indirect_write_xfer_start_reg:Reg_0x0FC40078 : 0x00000000 CortexA53_0: GEL Output: OSPI0__OSPI_CFG_VBUSP__VBP2APB_WRAP__OSPI_CFG_VBP__OSPI_FLASH_APB_REGS_indirect_write_xfer_num_bytes_reg:Reg_0x0FC4007C : 0x00000000 CortexA53_0: GEL Output: OSPI0__OSPI_CFG_VBUSP__VBP2APB_WRAP__OSPI_CFG_VBP__OSPI_FLASH_APB_REGS_indirect_trigger_addr_range_reg:Reg_0x0FC40080 : 0x00000004 CortexA53_0: GEL Output: OSPI0__OSPI_CFG_VBUSP__VBP2APB_WRAP__OSPI_CFG_VBP__OSPI_FLASH_APB_REGS_flash_cmd_addr_reg:Reg_0x0FC40094 : 0x00800004 CortexA53_0: GEL Output: OSPI0__OSPI_CFG_VBUSP__VBP2APB_WRAP__OSPI_CFG_VBP__OSPI_FLASH_APB_REGS_flash_rd_data_lower_reg:Reg_0x0FC400A0 : 0x00000021 CortexA53_0: GEL Output: OSPI0__OSPI_CFG_VBUSP__VBP2APB_WRAP__OSPI_CFG_VBP__OSPI_FLASH_APB_REGS_flash_rd_data_upper_reg:Reg_0x0FC400A4 : 0x00000000 CortexA53_0: GEL Output: OSPI0__OSPI_CFG_VBUSP__VBP2APB_WRAP__OSPI_CFG_VBP__OSPI_FLASH_APB_REGS_flash_wr_data_lower_reg:Reg_0x0FC400A8 : 0x00000020 CortexA53_0: GEL Output: OSPI0__OSPI_CFG_VBUSP__VBP2APB_WRAP__OSPI_CFG_VBP__OSPI_FLASH_APB_REGS_flash_wr_data_upper_reg:Reg_0x0FC400AC : 0x00000000 CortexA53_0: GEL Output: OSPI0__OSPI_CFG_VBUSP__VBP2APB_WRAP__OSPI_CFG_VBP__OSPI_FLASH_APB_REGS_polling_flash_status_reg:Reg_0x0FC400B0 : 0x00000000 CortexA53_0: GEL Output: OSPI0__OSPI_CFG_VBUSP__VBP2APB_WRAP__OSPI_CFG_VBP__OSPI_FLASH_APB_REGS_phy_master_control_reg:Reg_0x0FC400B8 : 0x00800000 CortexA53_0: GEL Output: OSPI0__OSPI_CFG_VBUSP__VBP2APB_WRAP__OSPI_CFG_VBP__OSPI_FLASH_APB_REGS_dll_observable_lower_reg:Reg_0x0FC400BC : 0x00FF81F9 CortexA53_0: GEL Output: OSPI0__OSPI_CFG_VBUSP__VBP2APB_WRAP__OSPI_CFG_VBP__OSPI_FLASH_APB_REGS_dll_observable_upper_reg:Reg_0x0FC400C0 : 0x00000000 CortexA53_0: GEL Output: OSPI0__OSPI_CFG_VBUSP__VBP2APB_WRAP__OSPI_CFG_VBP__OSPI_FLASH_APB_REGS_opcode_ext_lower_reg:Reg_0x0FC400E0 : 0x0302FA00 CortexA53_0: GEL Output: OSPI0__OSPI_CFG_VBUSP__VBP2APB_WRAP__OSPI_CFG_VBP__OSPI_FLASH_APB_REGS_opcode_ext_upper_reg:Reg_0x0FC400E4 : 0x06F90000 CortexA53_0: GEL Output: OSPI0__OSPI_CFG_VBUSP__VBP2APB_WRAP__OSPI_CFG_VBP__OSPI_FLASH_APB_REGS_module_id_reg:Reg_0x0FC400FC : 0x03000300 CortexA53_0: GEL Output: OSPI0__OSPI_CFG_VBUSP__MMR__MMRVBP__REGS_PID:Reg_0x0FC44000 : 0x68747900 CortexA53_0: GEL Output: OSPI0__OSPI_CFG_VBUSP__MMR__MMRVBP__REGS_CTRL:Reg_0x0FC44004 : 0x00000000 CortexA53_0: GEL Output: OSPI0__OSPI_CFG_VBUSP__MMR__MMRVBP__REGS_STAT:Reg_0x0FC44008 : 0x00000002

BR

Ryan

尊敬的 Linjun:

寄存器值如下所示:

CortexA53_0: GEL Output: OSPI0__OSPI_CFG_VBUSP__VBP2APB_WRAP__OSPI_CFG_VBP__OSPI_FLASH_APB_REGS_config_reg:Reg_0x0FC40000 : 0x80483841 CortexA53_0: GEL Output: OSPI0__OSPI_CFG_VBUSP__VBP2APB_WRAP__OSPI_CFG_VBP__OSPI_FLASH_APB_REGS_dev_instr_rd_config_reg:Reg_0x0FC40004 : 0x0802006C CortexA53_0: GEL Output: OSPI0__OSPI_CFG_VBUSP__VBP2APB_WRAP__OSPI_CFG_VBP__OSPI_FLASH_APB_REGS_dev_instr_wr_config_reg:Reg_0x0FC40008 : 0x00020032 CortexA53_0: GEL Output: OSPI0__OSPI_CFG_VBUSP__VBP2APB_WRAP__OSPI_CFG_VBP__OSPI_FLASH_APB_REGS_dev_delay_reg:Reg_0x0FC4000C : 0x0A0A0A0A CortexA53_0: GEL Output: OSPI0__OSPI_CFG_VBUSP__VBP2APB_WRAP__OSPI_CFG_VBP__OSPI_FLASH_APB_REGS_rd_data_capture_reg:Reg_0x0FC40010 : 0x00000027 CortexA53_0: GEL Output: OSPI0__OSPI_CFG_VBUSP__VBP2APB_WRAP__OSPI_CFG_VBP__OSPI_FLASH_APB_REGS_dev_size_config_reg:Reg_0x0FC40014 : 0x00101003 CortexA53_0: GEL Output: OSPI0__OSPI_CFG_VBUSP__VBP2APB_WRAP__OSPI_CFG_VBP__OSPI_FLASH_APB_REGS_sram_partition_cfg_reg:Reg_0x0FC40018 : 0x0000003F CortexA53_0: GEL Output: OSPI0__OSPI_CFG_VBUSP__VBP2APB_WRAP__OSPI_CFG_VBP__OSPI_FLASH_APB_REGS_ind_AHB_addr_trigger_reg:Reg_0x0FC4001C : 0x00000000 CortexA53_0: GEL Output: OSPI0__OSPI_CFG_VBUSP__VBP2APB_WRAP__OSPI_CFG_VBP__OSPI_FLASH_APB_REGS_dma_periph_config_reg:Reg_0x0FC40020 : 0x00000000 CortexA53_0: GEL Output: OSPI0__OSPI_CFG_VBUSP__VBP2APB_WRAP__OSPI_CFG_VBP__OSPI_FLASH_APB_REGS_remap_addr_reg:Reg_0x0FC40024 : 0x00000000 CortexA53_0: GEL Output: OSPI0__OSPI_CFG_VBUSP__VBP2APB_WRAP__OSPI_CFG_VBP__OSPI_FLASH_APB_REGS_mode_bit_config_reg:Reg_0x0FC40028 : 0x00000000 CortexA53_0: GEL Output: OSPI0__OSPI_CFG_VBUSP__VBP2APB_WRAP__OSPI_CFG_VBP__OSPI_FLASH_APB_REGS_sram_fill_reg:Reg_0x0FC4002C : 0x00000000 CortexA53_0: GEL Output: OSPI0__OSPI_CFG_VBUSP__VBP2APB_WRAP__OSPI_CFG_VBP__OSPI_FLASH_APB_REGS_tx_thresh_reg:Reg_0x0FC40030 : 0x00000001 CortexA53_0: GEL Output: OSPI0__OSPI_CFG_VBUSP__VBP2APB_WRAP__OSPI_CFG_VBP__OSPI_FLASH_APB_REGS_rx_thresh_reg:Reg_0x0FC40034 : 0x00000001 CortexA53_0: GEL Output: OSPI0__OSPI_CFG_VBUSP__VBP2APB_WRAP__OSPI_CFG_VBP__OSPI_FLASH_APB_REGS_write_completion_ctrl_reg:Reg_0x0FC40038 : 0x000340FF CortexA53_0: GEL Output: OSPI0__OSPI_CFG_VBUSP__VBP2APB_WRAP__OSPI_CFG_VBP__OSPI_FLASH_APB_REGS_no_of_polls_bef_exp_reg:Reg_0x0FC4003C : 0xFFFFFFFF CortexA53_0: GEL Output: OSPI0__OSPI_CFG_VBUSP__VBP2APB_WRAP__OSPI_CFG_VBP__OSPI_FLASH_APB_REGS_irq_status_reg:Reg_0x0FC40040 : 0x00000000 CortexA53_0: GEL Output: OSPI0__OSPI_CFG_VBUSP__VBP2APB_WRAP__OSPI_CFG_VBP__OSPI_FLASH_APB_REGS_irq_mask_reg:Reg_0x0FC40044 : 0x00000000 CortexA53_0: GEL Output: OSPI0__OSPI_CFG_VBUSP__VBP2APB_WRAP__OSPI_CFG_VBP__OSPI_FLASH_APB_REGS_lower_wr_prot_reg:Reg_0x0FC40050 : 0x00000000 CortexA53_0: GEL Output: OSPI0__OSPI_CFG_VBUSP__VBP2APB_WRAP__OSPI_CFG_VBP__OSPI_FLASH_APB_REGS_upper_wr_prot_reg:Reg_0x0FC40054 : 0x00000000 CortexA53_0: GEL Output: OSPI0__OSPI_CFG_VBUSP__VBP2APB_WRAP__OSPI_CFG_VBP__OSPI_FLASH_APB_REGS_wr_prot_ctrl_reg:Reg_0x0FC40058 : 0x00000000 CortexA53_0: GEL Output: OSPI0__OSPI_CFG_VBUSP__VBP2APB_WRAP__OSPI_CFG_VBP__OSPI_FLASH_APB_REGS_indirect_read_xfer_ctrl_reg:Reg_0x0FC40060 : 0x00000000 CortexA53_0: GEL Output: OSPI0__OSPI_CFG_VBUSP__VBP2APB_WRAP__OSPI_CFG_VBP__OSPI_FLASH_APB_REGS_indirect_read_xfer_watermark_reg:Reg_0x0FC40064 : 0x00000000 CortexA53_0: GEL Output: OSPI0__OSPI_CFG_VBUSP__VBP2APB_WRAP__OSPI_CFG_VBP__OSPI_FLASH_APB_REGS_indirect_read_xfer_start_reg:Reg_0x0FC40068 : 0x00000000 CortexA53_0: GEL Output: OSPI0__OSPI_CFG_VBUSP__VBP2APB_WRAP__OSPI_CFG_VBP__OSPI_FLASH_APB_REGS_indirect_read_xfer_num_bytes_reg:Reg_0x0FC4006C : 0x00000000 CortexA53_0: GEL Output: OSPI0__OSPI_CFG_VBUSP__VBP2APB_WRAP__OSPI_CFG_VBP__OSPI_FLASH_APB_REGS_indirect_write_xfer_ctrl_reg:Reg_0x0FC40070 : 0x00000000 CortexA53_0: GEL Output: OSPI0__OSPI_CFG_VBUSP__VBP2APB_WRAP__OSPI_CFG_VBP__OSPI_FLASH_APB_REGS_indirect_write_xfer_watermark_reg:Reg_0x0FC40074 : 0xFFFFFFFF CortexA53_0: GEL Output: OSPI0__OSPI_CFG_VBUSP__VBP2APB_WRAP__OSPI_CFG_VBP__OSPI_FLASH_APB_REGS_indirect_write_xfer_start_reg:Reg_0x0FC40078 : 0x00000000 CortexA53_0: GEL Output: OSPI0__OSPI_CFG_VBUSP__VBP2APB_WRAP__OSPI_CFG_VBP__OSPI_FLASH_APB_REGS_indirect_write_xfer_num_bytes_reg:Reg_0x0FC4007C : 0x00000000 CortexA53_0: GEL Output: OSPI0__OSPI_CFG_VBUSP__VBP2APB_WRAP__OSPI_CFG_VBP__OSPI_FLASH_APB_REGS_indirect_trigger_addr_range_reg:Reg_0x0FC40080 : 0x00000004 CortexA53_0: GEL Output: OSPI0__OSPI_CFG_VBUSP__VBP2APB_WRAP__OSPI_CFG_VBP__OSPI_FLASH_APB_REGS_flash_command_ctrl_mem_reg:Reg_0x0FC4008C : 0x00000000 CortexA53_0: GEL Output: OSPI0__OSPI_CFG_VBUSP__VBP2APB_WRAP__OSPI_CFG_VBP__OSPI_FLASH_APB_REGS_flash_cmd_ctrl_reg:Reg_0x0FC40090 : 0x11008000 CortexA53_0: GEL Output: OSPI0__OSPI_CFG_VBUSP__VBP2APB_WRAP__OSPI_CFG_VBP__OSPI_FLASH_APB_REGS_flash_cmd_addr_reg:Reg_0x0FC40094 : 0x00800004 CortexA53_0: GEL Output: OSPI0__OSPI_CFG_VBUSP__VBP2APB_WRAP__OSPI_CFG_VBP__OSPI_FLASH_APB_REGS_flash_rd_data_lower_reg:Reg_0x0FC400A0 : 0x00000021 CortexA53_0: GEL Output: OSPI0__OSPI_CFG_VBUSP__VBP2APB_WRAP__OSPI_CFG_VBP__OSPI_FLASH_APB_REGS_flash_rd_data_upper_reg:Reg_0x0FC400A4 : 0x00000000 CortexA53_0: GEL Output: OSPI0__OSPI_CFG_VBUSP__VBP2APB_WRAP__OSPI_CFG_VBP__OSPI_FLASH_APB_REGS_flash_wr_data_lower_reg:Reg_0x0FC400A8 : 0x00000020 CortexA53_0: GEL Output: OSPI0__OSPI_CFG_VBUSP__VBP2APB_WRAP__OSPI_CFG_VBP__OSPI_FLASH_APB_REGS_flash_wr_data_upper_reg:Reg_0x0FC400AC : 0x00000000 CortexA53_0: GEL Output: OSPI0__OSPI_CFG_VBUSP__VBP2APB_WRAP__OSPI_CFG_VBP__OSPI_FLASH_APB_REGS_polling_flash_status_reg:Reg_0x0FC400B0 : 0x00000000 CortexA53_0: GEL Output: OSPI0__OSPI_CFG_VBUSP__VBP2APB_WRAP__OSPI_CFG_VBP__OSPI_FLASH_APB_REGS_phy_configuration_reg:Reg_0x0FC400B4 : 0x00000000 CortexA53_0: GEL Output: OSPI0__OSPI_CFG_VBUSP__VBP2APB_WRAP__OSPI_CFG_VBP__OSPI_FLASH_APB_REGS_phy_master_control_reg:Reg_0x0FC400B8 : 0x00800000 CortexA53_0: GEL Output: OSPI0__OSPI_CFG_VBUSP__VBP2APB_WRAP__OSPI_CFG_VBP__OSPI_FLASH_APB_REGS_dll_observable_lower_reg:Reg_0x0FC400BC : 0x00000000 CortexA53_0: GEL Output: OSPI0__OSPI_CFG_VBUSP__VBP2APB_WRAP__OSPI_CFG_VBP__OSPI_FLASH_APB_REGS_dll_observable_upper_reg:Reg_0x0FC400C0 : 0x00000000 CortexA53_0: GEL Output: OSPI0__OSPI_CFG_VBUSP__VBP2APB_WRAP__OSPI_CFG_VBP__OSPI_FLASH_APB_REGS_opcode_ext_lower_reg:Reg_0x0FC400E0 : 0x0302FA00 CortexA53_0: GEL Output: OSPI0__OSPI_CFG_VBUSP__VBP2APB_WRAP__OSPI_CFG_VBP__OSPI_FLASH_APB_REGS_opcode_ext_upper_reg:Reg_0x0FC400E4 : 0x06F90000 CortexA53_0: GEL Output: OSPI0__OSPI_CFG_VBUSP__VBP2APB_WRAP__OSPI_CFG_VBP__OSPI_FLASH_APB_REGS_module_id_reg:Reg_0x0FC400FC : 0x03000300 CortexA53_0: GEL Output: OSPI0__OSPI_CFG_VBUSP__MMR__MMRVBP__REGS_PID:Reg_0x0FC44000 : 0x68747900 CortexA53_0: GEL Output: OSPI0__OSPI_CFG_VBUSP__MMR__MMRVBP__REGS_CTRL:Reg_0x0FC44004 : 0x00000000 CortexA53_0: GEL Output: OSPI0__OSPI_CFG_VBUSP__MMR__MMRVBP__REGS_STAT:Reg_0x0FC44008 : 0x00000002BR

Ryan

您好、Ryan、

您能否修复一下适用于 AM64x 的 MCU PLUS SDK 10.01中的这个小错误?

在 ospi_LLD.h 第182行内、您能继续切换数据和 addr 的位置吗?

因此、定义应如下所示:

完成后、请重新编译库。

并运行您的代码。

为什么会发生这种变化?

函数定义应为 cmd、addr、数据遵循1s-1s、并且设置正确。

但是、在之前的 SDK 中、它会以 cmd、data、addr 的形式写入、这会使设置为1s-4s-1、而不是所需的1s-4s。

此致、

Vaibhav

您好、Ryan

[报价用户 id="490736" url="~/support/processors-group/processors/f/processors-forum/1450567/am6421-ospi-frame-is-split/5673431 #5673431"]您能回答来自 Lucas 的问题吗?

1. 间接模式下的读取操作被拆分为多个请求。[/QUOT]您是否有这方面的示波器捕获? 或者解释分割/重叠是什么?

此外、

此致

Karan

大家好、Lucas:

1. 我们在 A53上使用 OSPI、因此没有 MPU 配置、只有 MMU 设置。

2. MMU 配置如下:

MmuP_RegionConfig gMmuRegionConfig[CONFIG_MMU_NUM_REGIONS] =

{

{

.vaddr = 0x0u,

.paddr = 0x0u,

.size = 0x80000000u,

.attr = {

.accessPerm = MMUP_ACCESS_PERM_PRIV_RW_USER_NONE,

.privExecute = 1,

.userExecute = 0,

.shareable = MMUP_SHARABLE_OUTER,

.attrIndx = MMUP_ATTRINDX_MAIR0,

.global = 1

}

},

{

.vaddr = 0x70000000u,

.paddr = 0x70000000u,

.size = 0x200000u,

.attr = {

.accessPerm = MMUP_ACCESS_PERM_PRIV_RW_USER_NONE,

.privExecute = 1,

.userExecute = 0,

.shareable = MMUP_SHARABLE_OUTER,

.attrIndx = MMUP_ATTRINDX_MAIR7,

.global = 1

}

},

{

.vaddr = 0x80000000u,

.paddr = 0x80000000u,

.size = 0x80000000u,

.attr = {

.accessPerm = MMUP_ACCESS_PERM_PRIV_RW_USER_NONE,

.privExecute = 1,

.userExecute = 0,

.shareable = MMUP_SHARABLE_OUTER,

.attrIndx = MMUP_ATTRINDX_MAIR7,

.global = 1

}

},

{

.vaddr = 0x78100000u,

.paddr = 0x78100000u,

.size = 0x1000u,

.attr = {

.accessPerm = MMUP_ACCESS_PERM_PRIV_RW_USER_NONE,

.privExecute = 0,

.userExecute = 0,

.shareable = MMUP_SHARABLE_OUTER,

.attrIndx = MMUP_ATTRINDX_MAIR7,

.global = 1

}

},

{

.vaddr = 0x701D0000u,

.paddr = 0x701D0000u,

.size = 0x10000u,

.attr = {

.accessPerm = MMUP_ACCESS_PERM_PRIV_RW_USER_NONE,

.privExecute = 1,

.userExecute = 0,

.shareable = MMUP_SHARABLE_OUTER,

.attrIndx = MMUP_ATTRINDX_MAIR4,

.global = 1

}

},

};

3. 即使尝试访问的内存设置为不可缓存、问题仍然存在。

4. 关于寄存器转储、 我没有在 TI SDK 之外使用任何接口、也没有手动修改任何接口或寄存器。 因为我没有深入研究这方面的细节、所以我不能回答这个问题。

BR

Ryan

您好、 Ryan、

下面是一个向 ospi 接口发送数据的采样代码,您能检查一下并提供反馈吗? obbisouly、传输长度和内存属性被定义。 谢谢。

#define APP_OSPI_DATA_SIZE (2048)

uint8_t gOspiTxBuf[APP_OSPI_DATA_SIZE];

/*使用 DMA 时、读取缓冲区必须在缓存行对齐、尽管32B 已足够、但我们还是对齐到128B */

uint8_t gOspiRxBuf[APP_OSPI_DATA_SIZE]__ATTRY__(aligned (128U));

Linjun

尊敬的 Linjun:

即使内存属性设置为高速缓存对齐、问题仍然存在。

BR

Ryan

您好、Ryan、

今天我们的电话,我应该给你发送以下波形:

该波形如这两个事务中所示、出现在1片选低电平。

如何查看波形?

要查看波形、只需前往此网站并下载 Logic 2软件: https://www.saleae.com/pages/downloads

下载后、您可以保存附加的扩展名为.Sal 的波形、然后只需单击即可。 它将自动打开逻辑2软件并显示波形。

此致、

Vaibhav

有关如何在软件中启用 INDAC 读取的详细步骤:

完成后、请继续重建您的应用程序、这将确保将更改考虑在内。

在这里、您已经成功启用了 INDAC 读取。

此致、

Vaibhav

您好、Ryan、

[报价 userid="531612" url="~/support/processors-group/processors/f/processors-forum/1450567/am6421-ospi-frame-is-split/5683140 #5683140"]8d-8d-8d INDAC 从 OSPI NOR 闪存读取的128字节(我焊接的是针对具有 OSPI NOR 闪存的 TI EVM 完成的、之前焊接的波形是针对上述两个捕捉的波形、焊接是在具有 QSPI NOR 闪存的 TI EVM 上完成的)[ 注意: 我将在某个时间内发送相关波形]我已经使用 OSPI NOR 闪存器件 S28HS512T 完成了8D-8D-8D 模式的波形采集。

该波形适用于 INDAC 读取128个字节的数据。 读取的值是0、1、2、3、4...、 127.

发生这种情况时、发送两次0xEE 命令、然后我们读取值0、1、2、...、直到1芯片选择切换下的127。

e2e.ti.com/.../indirect_5F00_read_5F00_128bytes_5F00_8d_5F00_8d_5F00_8d.sal

此致、

Vaibhav