工具与软件:

你(们)好、

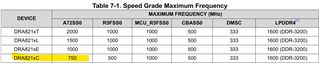

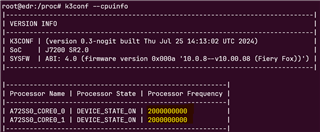

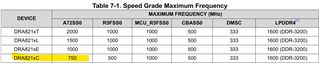

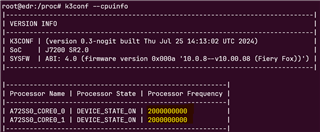

我们使用 DRA821xC 芯片、根据下面显示的数据表信息、最大频率为750MHz。 然而,当我使用 k2conf -- cpuinfo 时,我得到2GHz。 我的问题是如何获得实际的 CPU 频率、即 CPU 的运行频率? 谢谢。

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

工具与软件:

你(们)好、

我们使用 DRA821xC 芯片、根据下面显示的数据表信息、最大频率为750MHz。 然而,当我使用 k2conf -- cpuinfo 时,我得到2GHz。 我的问题是如何获得实际的 CPU 频率、即 CPU 的运行频率? 谢谢。

Charles

SDK 将默认频率设置为超集 T 速度等级器件。 您需要修改 SDK 以根据数据表频率进行配置。 此处提供了与此主题相关的常见问题解答:

此致、

Kyle

尊敬的 Kyle:

了解了我们需要更改用于-T 2GHz 速度的默认超集 SDK 频率设置以达到-C 750MHz 速度。

Q1:-C 速度部件是否支持2GHz? 或者、即使默认设置是2GHz、它也会运行750MHz?

问题2: DDR 和 PCIe 数据速率是否受此核心频率设置的影响(-C 速度与-T 速度)? 我的理解不正确吗?

Q3:在相同的资源工作负载下、-C 速度和-T 速度之间有多大的功耗差异?

谢谢

最大值

尊敬的 Charles:

使用 DevTool、您可通过以下项编辑 u-boot 方法:

devtool edit-recipe u-boot-ti-staging

或者、您也可以创建一个工作区:

devtool create-workspace u-boot-ti-staging

如果有自定义图层、则可以在类似于 以下内容的目录结构中创建 bbappend 和增补程序:

meta-example ├── recipes-bsp │ └── u-boot │ ├── u-boot-ti-staging-2024.04 │ │ ├── example.patch │ └── u-boot-ti-staging_2024.04.bbappend ...

您需要指定相关的 u-boot 版本。

此致!

Jared

尊敬的 Jared:

感谢您的答复。 我创建了一个工作区 u-boot-ti-staging、但在要修补的工作区中找不到 sbl_soc_cfg.h 文件。

build/workspace/sources/u-boot-ti-staging$ find -name sbl_soc_cfg.h -print build/workspace/sources/u-boot-ti-staging$

尊敬的 Jared:

很抱歉混淆。 我提到 sbl_soc_cfg.h 只是因为 Kyle 提供了参考建议来修补它(https://e2e.ti.com/support/processors-group/processors/f/processors-forum/1227640/faq-tda4vm-tda4vl-tda4al-tda4vh-dra821-how-can-we-make-the-jacinto-sdk-compatible-for-device-variants-yxz)。 根据您的反馈、我认为我应该修改 SPL 引导。 我需要将 A72 CPU 频率从默认的2GHz (超集芯片-T 速度等级)更改为芯片等级速度(我使用的是-C 速度750MHz)。

您能告诉我应该修补哪个文件 、以便我的 Linux 映像能够在750MHz 而不是默认的2GHz 频率下运行吗?

谢谢!

Charles

尊敬的 Charles:

您能查看以下主题/常见问题解答吗?

此致!

Jared

尊敬的 Jared:

感谢您提供信息。 在哪里可以找到 A72内核的器件树绑定文档?

我的 dts 文件(SDK 10.00.08)看起来与您在链接 e2e.ti.com/.../faq-dra821u-how-to-change-the-frequency-of-a72-and-r5f-cores-and-disable-one-a72-core 中提供的 u-boot 补丁不同。

对于 assigned-clock-rate 属性、u-boot 补丁会显示两个整数值、而在我的器件树文件中、有3个整数值。

diff --git a/arch/arm/dts/k3-j7200-r5-common-proc-board.dts b/arch/arm/dts/k3-j7200-r5-common-proc-board.dts index 6bfc322da2..059fdf26aa 100644 --- a/arch/arm/dts/k3-j7200-r5-common-proc-board.dts +++ b/arch/arm/dts/k3-j7200-r5-common-proc-board.dts @@ -33,7 +33,7 @@ <&k3_pds 202 TI_SCI_PD_EXCLUSIVE>; resets = <&k3_reset 202 0>; assigned-clocks = <&k3_clks 202 2>, <&k3_clks 61 1>; - assigned-clock-rates = <2000000000>, <200000000>; + assigned-clock-rates = <400000000>, <200000000>; ti,sci = <&dmsc>; ti,sci-proc-id = <32>; ti,sci-host-id = <10>;

我的设备树:

resets = <&k3_reset 202 0>;

clocks = <&k3_clks 61 1>, <&k3_clks 4 1>, <&k3_clks 202 2>;

clock-names = "gtc_clk", "msmc_clk", "arm_clk";

assigned-clocks = <&k3_clks 202 2>, <&k3_clks 61 1>, <&k3_clks 4 1>, <&k3_clks 323 0>;

assigned-clock-parents= <0>, <0>, <0>, <&k3_clks 323 2>;

assigned-clock-rates = <1000000000>, <200000000>, <1000000000>;

要使用的实际 CPU 频率是哪个值? 文档在哪里?

谢谢!

Charles

尊敬的 Charles:

感谢您提供信息。 在哪里可以找到 A72内核的器件树绑定文档?

[报价]A72位于: https://www.kernel.org/doc/Documentation/devicetree/bindings/arm/cpus.yaml 下

[/quote]要使用的实际 CPU 频率是哪个值? 文档在哪里?

[报价]时钟标识位于此处: https://software-dl.ti.com/tisci/esd/latest/5_soc_doc/j7200/clocks.html

时钟"202 2"对应于: DEV_A72SS0_CORE0_0_ARM_CLK_CLK、因此将该时钟设置为 750 MHz 将起作用。

以下是其他时钟标识:

- 0:DEV_GTC0_GTC_CLK

- 1: DEV_A72SS0_CORE0_MSMC_CLK

- 323 0: DEV_MAIN_PLL8_SEL_EXTWAVE_VD_CLK

此致!

Jared