工具/软件:

尊敬的专家

这是概念问题、需要仔细检查

我们有一个示例代码(复位隔离- MCU 域)、我想这是 FFI (无干扰)演示、不是吗?

当 MCU 进入 复位隔离(FFI?!)时、

(1)主域 外设和 MCU 域外设无法相互访问、不能

(2)任何 IPC 服务(例如:RPMSG)将被禁用、不是吗?

谢谢你。

Gibbs

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

工具/软件:

尊敬的专家

这是概念问题、需要仔细检查

我们有一个示例代码(复位隔离- MCU 域)、我想这是 FFI (无干扰)演示、不是吗?

当 MCU 进入 复位隔离(FFI?!)时、

(1)主域 外设和 MCU 域外设无法相互访问、不能

(2)任何 IPC 服务(例如:RPMSG)将被禁用、不是吗?

谢谢你。

Gibbs

我们有一个示例代码(复位隔离- MCU 域)、我想这是 FFI (无干扰)演示、不是吗?

[/报价]您好、Gibbs、

是的、您回答正确。

上述示例可用于展示在复位后 MCU 域仍可与主域隔离。

[报价 userid="533255" url="~/support/processors-group/processors/f/processors-forum/1468969/am620-q1-is-reset-isolation-for-mcu-domain-is-so-called-ffi-freedom-from-interference(1)主域 外设和 MCU 域外设无法相互访问、不能

[/报价]是、默认情况下、在复位隔离 MCU+SDK 示例中、跨域外设 的使用受到限制。

这样、IPC 就不会在内核之间运行。

但是、如果客户需要复位隔离以及 IPC 和跨域外设、那么我们可以将 MCU 域配置为部分隔离。

在此模式下、当主域获得复位并允许跨域外设使用时、MCU 内核仍将被隔离。

如果您控制下面的这些标志、则跨域外设 的使用将起作用、并且 MCU 内核在复位后与主域隔离。

pscMain2MCUDisable = 0;

/* Disabling MCU2Main PSC. This would restrict the MCU domain from accessing

Main domain peripherals/registers. Care must be taken no MCU domain cores access

Main domain registers after this */

pscMCU2MainDisable = 0;

此致、

Anil.

您好、Gibbs、

如果客户想要在 M4F 和 A53之间实现复位隔离和 IPC、那么他们应该按照以下步骤操作、这适用于他们。

如果您需要任何帮助、请告诉我

[报价 userid="525901" url="~/support/processors-group/processors/f/processors-forum/1468969/am620-q1-is-reset-isolation-for-mcu-domain-is-so-called-ffi-freedom-from-interference/5639858 #5639858"]但是、如果客户需要复位隔离以及 IPC 和跨域外设、那么我们可以将 MCU 域配置为部分隔离。

在此模式下、当主域获得复位并允许跨域外设使用时、MCU 内核仍将被隔离。

如果您控制下面的这些标志、则跨域外设 的使用将起作用、并且 MCU 内核在复位后与主域隔离。

[/报价]此致、

Anil.

尊敬的 Devin:

现在我了解了问题。 实际上、DDR 存储器上提供了 Linux 表 IPC 信息。

一旦复位 MAIN 域、DDR 内容也会丢失。 因此、清除此缓冲区后、IPC 将不工作。

后续步骤:

要解决此问题、您已经从 MCU M4F 复位主域。 因此、首先复制 Linux 资源表数据(DDR)并将 DDR 数据移动到 M4F DRAM 存储器。 务必复位 MAIN 域。

启动 SBL 后 、将 M4F DRAM 数据复制到 IPC 资源表存储器的 DDR。

以下链接也与 AM62A 器件上所面临的问题类似、并根据上述解决方案进行了修复。

如果您仍需要任何帮助、请查看并告诉我。

此致、

Anil.

您好 Anil、

我也想问、

启动 SBL 后 、将 M4F DRAM 数据复制到 IPC 资源表内存的 DDR 中。

如何在 Uboot 启动时复制数据?

此致、

Devin。

嗨、Anil

感谢您的建议

关注您的评论、

>> 将 M4F DRAM 数据复制到 IPC 资源表存储器的 DDR。

参考此链接、

我假设我们没有用于"IPC 资源表"备份或恢复的软件 API、因此我们需要自行实现此功能、不是吗?

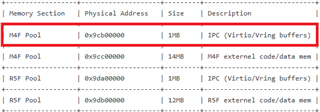

我认为 IPC 资源表位于地址 0x9cb00000 + 1MB 长度中、不是吗?

我认为故事应该如下所示、其中包含"FFI + MCU RESET A Core"

(1)在 MCU SW 中设置这些参数。 这可能会让 MCU M4内核警告复位内核

pscMain2MCUDisable = 0; pscMCU2MainDisable = 0

(2)如果一个核心认知系统转至 FFI、则核心(Linux)应随时备份任何存储中的"IPC 资源表"。 (例如 eMMC)

(3) M 内核触发器发生内核复位后、U-boot 或 SBL (TIBOOT3)应 首先将"IPC 资源表"恢复到 DDR

(4)基本而言、 在这种情况下、M 内核不需要重新加载固件并保持 RPMsg 通信

如果有问题、请纠正我。

再次感谢您

Gibbs

您好、Gibbs、

[报价 userid="533255" url="~/support/processors-group/processors/f/processors-forum/1468969/am620-q1-is-reset-isolation-for-mcu-domain-is-so-called-ffi-freedom-from-interference/5652168 #5652168"](2)如果一个核心认知系统转至 FFI、则核心(Linux)应随时备份任何存储中的"IPC 资源表"。 (例如 eMMC)

[/报价]上述步骤正确、但我们需要更改一些更改。

[报价 userid="533255" url="~/support/processors-group/processors/f/processors-forum/1468969/am620-q1-is-reset-isolation-for-mcu-domain-is-so-called-ffi-freedom-from-interference/5652168 #5652168"](3) M 内核触发器发生内核复位后、U-boot 或 SBL (TIBOOT3)应 首先将"IPC 资源表"恢复到 DDR

[/报价]是的、您回答正确。 可以在 U-boot 或 SBL 中进行此更改。

如果 客户在 U-boot 中遇到任何问题并在 A53核心应用程序中执行相同的步骤也是可以的。

确保在 Linux 内核将 IPC 消息发送到 M4F 内核之前、IPC 表数据必须放置在 DDR 中。

[报价 userid="533255" url="~/support/processors-group/processors/f/processors-forum/1468969/am620-q1-is-reset-isolation-for-mcu-domain-is-so-called-ffi-freedom-from-interference/5652168 #5652168"]我认为 IPC 资源表位于地址 0x9cb00000 + 1MB 长度中、不是吗?

我认为故事应该如下所示、其中包含"FFI + MCU RESET A Core"

[/报价]我们需要备份足够的4KB 存储器、并且必须从以下地址开始地址位置

/*当 M4内核提前使用 Linux 引导时、资源表必须放置在 DDR_IPC_resource_table_linux 的开头*/

DDR_IPC_resource_table_linux:origin = 0x9CC00000、length = 0x1000

如果您遇到任何问题、请告诉我。

此致、

Anil.

您好 Anil、

我将在 M4内核上执行复制操作。

步骤:

1.使用 memcpy()访问0x9CC00000备份资源表。

2.配置隔离模型并调用 SOC_generateSwWarmResetMainDomainFromMcuDomain()重置主域。

3.使用 memcpy()恢复资源表。

但是、RPMSG 在主域复位后仍然无法重新通信。

步骤是否正确?

此致、

Devin。

尊敬的 Devin:

无法直接从 M4F 内核访问 DDR 内存。

因此、在使用 DDR 存储器时需要使用 RAT 配置。

有关如何使用 M4F 内核的 DDR、请按照以下常见问题解答中的步骤操作。

此致、

Anil.

尊敬的 Devin:

请阅读常见问题解答、这里提供了所有步骤。

常见问题解答中还附加了一个示例。

我们需要将 DDR 存储器添加到 MPU 区域设置中。

然后,只需 将 DDR 内存位置(9cc00000 )传递给 AddrTranslateP_getLocalAddr API。

将数据移入本地地址。

此致、

Anil.

你好 Anil、

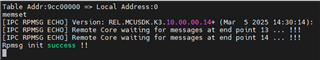

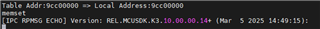

感谢您的回复、现在它打印:表 Addr:9cc00000 =>本地地址:9cc00000、但 RPMSG 仍然无法恢复通信。

让我告诉您我的关键步骤(基于我已配置的 RAT 和 MPU):

1.rp Message_Resource linuxResourceTable_back、使用此结构备份资源表。

2.memcpy (&linuxResourceTable_back、localAddr、sizeof (linuxResourceTable_back))、备份资源表。

SOC_enableResetSealization (pscMain2MCUDisable、pscMCU2MainDisable、psMCU2DMDisable、debugIsolationEnable)、参数 分别为1、0、0、1。

调用 SOC_generateSwarmResetMainDomainFromMcuDomain API (3和4的操作与示例一致)。

5.memcpy (localAddr、&linuxResourceTable_back、sizeof (linuxResourceTable_back))、恢复资源表的数据。

我想问您、我的步骤有什么问题? 或者我还需要做什么。

此致、

Devin

您好 Anil、

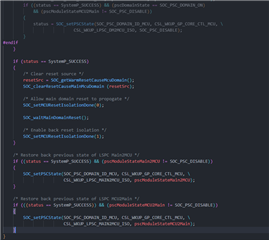

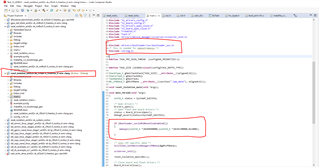

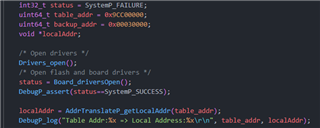

1.第一幅图像是示例代码,第二幅图像是我的代码。

我将 pscMCU2MainDisable 和 psMCU2DMDisable 的值设置为0、因为这些参数的值为1会导致看不到后续日志。

仅使用重置隔离代码共享 M4F 内核示例以查看代码更改

。

。

2.我们在 Uboot 阶段启动 M4内核。

这是您正在使用的引导模式

版本为10.00.00.14。

您正在使用哪个版本的 MCU+SDK

此致、

Devin。

您好 Anil、

1.在上面的第二个映像中、使用 memcopy 备份资源表、并在复位 SOC 后恢复资源表。

您在哪里对 Linux 表执行 memcopy 操作以及重置发生后它们如何恢复

我真的很抱歉。 由于咨询安全和公司法规、我无法与您共享整个项目、但我可以与您共享我使用的测试代码。 我将 RPMSG 例程与热复位例程组合在一起、以测试复位后是否可以恢复通信。

引导模式为 eMMC。

我想问哪种引导模式是 OSPI 或 eMMC。 或 SD 引导模式?

此致、

Devin。

尊敬的 Devin:

也请分享 resetReqIsr 函数的片段。

如以上注释所示、本地地址在0x9CC00000位置具有 DDR 内容。

因此、我不会检查您的 RAT 和 MPU 区域设置。 如果可能、请共享它们。 我也可以看看它们。

您需要分配一个4KB 的专用内存位置、用于将 DDR Linux 表存储在 M4F RAM 内存中、并且无法由 M4F 应用程序使用该4KB 内存。

这种方法对您来说是否合适?

此致、

Anil.

您好 Anil、

1.我没有对 resetRealsr 函数做任何更改。

也请分享 resetReqIsr 函数的片段。

2.代码后面: localAddr = AddrTranslateP_getLocalAddr (table_addr ) ;

日志打印: 表地址:0x9CC00000 =>本地地址:0x9CC00000、此地址转换是否正确?

本地地址的 DDR 内容位于0x9CC00000位置。

我将分享所有 RAT 和 MPU 配置。

检查您的 RAT 和 MPU 区域设置

老鼠:

MPU:

4.我想问如何详细地做。 它是否应该在 linker.cmd 中配置、或者它应该在代码中分配4K 空间、还是以其他方式分配?

分配一个4KB 的专用内存位置、用于将 DDR Linux 表存储到 M4F RAM 中

此致、

Devin。

尊敬的 Devin:

上述更改的当前代码不起作用、因为数据将从 DDR 复制到 M4F RAM。

但是、我们不知道此重置是否已完全传播。

如果 SoC 进行复位、则从 RBL→SBL→Application 序列开始。

在此过程中、我们必须等待 DDR 初始化。

DDR 初始化完成后、我们需要将本地 M4F 存储器移动到 DDR。

此步骤应在 A53内核运行之前的 SBL 阶段2执行。

步骤1:定义4KB 的存储器来存储 Linux 表

修改链接器命令文件以定义专用的存储器区域:

M4F_DRAM_LINUX_BAKUP_TABLE : ORIGIN = 0x00030000 , LENGTH = 0x1000

M4F_DRAM : ORIGIN = 0x00031000 , LENGTH = 0xF000

.bss.ipc_backup_linux_table (NOLOAD) : {} > M4F_DRAM_LINUX_BAKUP_TABLE

步骤2:将 DDR 地址空间转换为"Local Memory"视图

使用 RAT (区域地址转换)和地址转换函数将 DDR 地址空间转换为本地存储器。

•上述 RAT 配置似乎正确。

•您可以通过检查本地存储器地址是否正确反映 DDR 内容来验证它。

步骤3:从 MCU 域访问主域外设

•MAIN2MCU 和 MCU2MAIN 桥标志设置正确、无需更改。

•所有 MAIN2MCU 和 MCU2MAIN 桥接标志保持不变。

步骤4:将 DDR 内容移动到 M4F 内核

•初始化 M4F 内核后、将 DDR 内容复制到 M4F 内核。

•这只需执行一次、而不需要重复执行。

步骤5:将 M4F DRAM 存储器移动到 DDR

•此步骤应在 Linux 内核运行(SBL 阶段2)之前执行。

M4F DRAM 存储器位于 M4F 存储器视图中的0x30000。

当 DM R5F 需要使用此存储器时、其参考地址应为0x05040000。

按如下方式修改代码:

#define IPC_LINUX_TABLe_BACKUP

if (Bootloader_socIsMCUResetIsoEnabled())

{

#ifdef IPC_LINUX_TABLe_BACKUP

memcpy(0x05040000,0x9CC00000,0x1000);

#endif

}

步骤6:编译并刷写软件

•编译 SBL 和应用程序。

•闪存 SBL 和应用程序

如果您需要进一步说明、请告诉我。

请分享测试结果。

此致、

Anil

您好 Anil、

遗憾的是、测试结果仍然相同。

它从 RBL→SBL→Application Sequence 开始。

我们的启动过程与此不同、我们使用 SPL、这种区分是否会导致测试结果出现偏差?

此步骤应在 Linux 内核运行前执行

如何通过 Bootloader_socIsMCUResetIsoEnabled 函数确定当前阶段是否在 Linux 内核运行之前?

此致、

Devin。

尊敬的 Devin:

从 M4F DRAM 存储器到 DDR 步骤的数据需要在传播复位后完成。

如果此步骤不正确、则 IPC 将无法运行。

步骤5:将 M4F DRAM 存储器移动到 DDR

[/报价]因此、您可以向 A53内核应用程序而不是 SBL 或 SPL 执行此步骤吗?

步骤4:将 DDR 内容移动到 M4F 内核

•初始化 M4F 内核后、将 DDR 内容复制到 M4F 内核。

•这只需执行一次、不需要重复执行。您能否确认 Linux 表 DDR 内容已移动到 M4F 存储器位置0x30000?

此致、

Anil.

[/quote]

您好 Anil、

那么、您是否可以向 A53核心应用程序(而不是 SBL 或 SPL)执行此步骤?

您的意思是让我在 uboot 阶段执行步骤5?

我发现了另一个 问题 :似乎在代码执行期间, resetRealsr 函数未被调用。

此致、

Devin。

尊敬的 Devin:

[引述 userid="628094" url="~/support/processors-group/processors/f/processors-forum/1468969/am620-q1-is-reset-isolation-for-mcu-domain-is-so-called-ffi-freedom-from-interference/5672376 #5672376"]您的意思是让我在 uboot 阶段执行步骤5?

[/报价]我说的是 A53核心 Linux 应用程序。

此致、

Anil.

您好、Anil & Devin

由于个人商务旅行、很抱歉晚才加入讨论。

嗨、 Devin。

根据您的"系统设计"、您需要考虑两个方面:

(1)如果复位隔离用于"仅 MCU 模式"、则可以备份 MCU SRAM 中的"IPC 资源表"、因为 MCU 始终处于活动状态。

(2)如果您的功能还在进入深度睡眠模式然后唤醒、您可能需要将"IPC 资源表"和"MCU 上下文"备份到 eMMC、因为 SoC 和 MCU 也会关断、所以您将丢失所有数据。

据我所知、您的系统是 eMMC 引导

根据以前的讨论、我认为这是以"项目1"为基础的。 由于您的情况是处于仅 MCU 模式且部分 隔离、您尝试向复位 SoC (A53)发出警告、并参阅 Linux 重新启动、因此 RPMSG 失败的根本原因似乎是引导加载程序 在重新启动时没有加载"备份""IPC 资源表"。

在与我们的 AE 会面之前、我建议您创建另一个"新项目"、进行测试并与我们分享。 因为我们需要逐步检查它。

*您如何确保备份正确的"IPC 资源表"? 如何检查它? 任何错误?

*唤醒 SoC (A53)后、如何在 A53引导时恢复"IPC 资源表"? 我看到 Anil 已经给了您一些注释、它似乎也修改了 u-boot (tiboot3)中的一些代码

建议先完成项目1并测试确定、然后深入讨论项目2用户案例。

您也可以将您的项目发送给我。

您好、Anil

如果我说了什么错误,请纠正我。

非常感谢

Gibbs

您好、Gibbs/Dev、

我看了 AM62X 的引导流程。 请查看下面的链接。

在这里、DM 固件在 b-boot 和 A53 Linux 启动之前运行。

因此、我们不是在 SBL 或 u-boot 中执行第5步、而是可以将此步骤移至 DM 固件应用程序。

这也对您有利。

现在、除了步骤5和步骤6之外、您应该执行以下相同的步骤。

第5步:

以您已在应用中使用的 DM R5F 示例为例。

在该应用程序中、在所有驱动程序初始化之后执行 memcpy 调用。

客户还需要在 DM R5F 应用程序中集成#include 更改以修复编译器 erros。

编译 DM R5F 应用程序

第6步:

完成 DM R5F 应用后、

刷写更新后的 DM 应用程序。

请按照以下所有步骤操作。 如果 在客户硬件中仍然无法正常工作、我可以连接到联机调试。

步骤1:定义4KB 的存储器来存储 Linux 表

修改链接器命令文件以定义专用的存储器区域:

全屏1.2.3.M4F_DRAM_LINUX_BAKUP_TABLE : origin = 0x00030000、长度= 0x1000M4F_DRAM:原点= 0x00031000、长度= 0xF000.bss.ipc_backup_linux_table (NoLoad):{}> M4F_DRAM_linux_BAKUP_TABLEXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXM4F_DRAM_LINUX_BAKUP_TABLE : ORIGIN = 0x00030000 , LENGTH = 0x1000 M4F_DRAM : ORIGIN = 0x00031000 , LENGTH = 0xF000 .bss.ipc_backup_linux_table (NOLOAD) : {} > M4F_DRAM_LINUX_BAKUP_TABLE步骤2:将 DDR 地址空间转换为"Local Memory"视图

使用 RAT (区域地址转换)和地址转换函数将 DDR 地址空间转换为本地存储器。

•上述 RAT 配置似乎正确。

•您可以通过检查本地存储器地址是否正确反映 DDR 内容来验证它。步骤3:从 MCU 域访问主域外设

•MAIN2MCU 和 MCU2MAIN 桥标志设置正确、无需更改。

•所有 MAIN2MCU 和 MCU2MAIN 桥接标志保持不变。步骤4:将 DDR 内容移动到 M4F 内核

•初始化 M4F 内核后、将 DDR 内容复制到 M4F 内核。

•这只需执行一次、而不需要重复执行。[/报价]

此致、

Anil.

嗨、 Devin

我想您需要先参考这两个链接、因为我认为您可能遇到 SBL/SPL 引导的概念问题。

我认为 Anil 是对的、

主域(SoC)复位后、它将重新加载 DM R5 FW 和 SYSFW、然后在稍后启动 SPL (u-boot)。

因此、最好的方法(时序)是尝试恢复 IPC 资源表、它位于 DM R5中。

因为在此步骤中、DDR 已经完成初始化。

顺便说一下、我没有收到幻灯片(PPT)

我可以在收到幻灯片时安排与您的另一次个人会议。

Gibbs

尊敬的 Devin:

添加的补丁不会给低功耗运行模式带来任何问题、这只是在 DM FW 初始化期间、而不是在运行时将数据从 DDR 存储器移动到 M4F RAM。

通常、如果在应用程序中使用 MCU+SDK 10版本、则以以下路径中的 DM 示例为例。

C:\ti\mcu_plus_sdk_am62x_10_00_00_14\examples\drivers\ipc\ipc_rpmsg_echo\am62x-sk

第5步:

以您已在应用中使用的 DM R5F 示例为例。

在该应用程序中、在所有驱动程序初始化之后执行 memcpy 调用。

客户还需要在 DM R5F 应用程序中集成#include 更改以修复编译器 erros。

编译 DM R5F 应用程序

[/报价]稍后、将上述补丁添加到 DM R5F 应用中。

编译 DM R5F 应用程序

最后、从 Linux 内核加载 DM R5F 更新 bin 文件。

https://dev.ti.com/tirex/explore/node?node=A__AXsPVjrUN0EAU1ezb.8iuQ__AM62-ACADEMY__uiYMDcq__LATEST

此致、

Anil.

你好 Anil / Gibbs、

[报价 userid="525901" url="~/support/processors-group/processors/f/processors-forum/1468969/am620-q1-is-reset-isolation-for-mcu-domain-is-so-called-ffi-freedom-from-interference/5693550 #5693550"]通常、如果在应用程序中使用 MCU+SDK 10版本、则以以下路径中的 DM 示例为例。

C:\ti\mcu_plus_sdk_am62x_10_00_00_14\examples\drivers\ipc\ipc_rpmsg_echo\am62x-sk

[/报价]我们使用的示例具有与您的示例不同的路径、

C:\ti\mcu_plus_sdk_am62x_10_00_00_14\examples\drivers\ipc\ipc_rpmsg_echo_linux\am62x-sk-lp\r5fss0-0_freeRTOS

我可以询问此路径是否也可以?

[报价 userid="525901" url="~/support/processors-group/processors/f/processors-forum/1468969/am620-q1-is-reset-isolation-for-mcu-domain-is-so-called-ffi-freedom-from-interference/5693550 #5693550"]最后、从 Linux 内核加载 DM R5F 更新 bin 文件。

[/报价]我们应该将编译?后生成的.out 文件推送到哪个目录

@吉布斯,我想在这里回答你的问题 PPT:

[Gibbs]:为什么不使用 uint64_t?? 是不是错了?

从日志中可以看到、如果使用 uint64_t、转换后的地址输出为0。

但如果我使用 uint32_t、其转换的地址为0x9CC00000。

[Gibbs]:为什么不使用 Rpmessage_Resource memcopy?

如何擦除 Rpmessage_Resource 中的 DDR 表、以及检查 IPC 是否正常工作? 如果 IPC 运行失败、则表示复制正确的存储器区域。

我打印 Rpmessage_Resource 表的地址、实际上是0x9CC00000。

我使用了测试方法。当我擦除 localAddr 时、RPMessage 无法初始化。

从日志中可以看到、地址正确。

此致、

Devin。

我可以询问此路径是否也可以?

[/报价]尊敬的 Devin:

您可以采用上述示例、这很好。

[/quote]@吉布斯,我想在这里回答你的问题 PPT:

[Gibbs]:为什么不使用 uint64_t?? 是不是错了?

[/报价]请使用32位。

此致、

Anil.

嗨、Anil

因为这种讨论环境太长、所以我尝试完成关键步骤、以确保您和我们都有相同的想法。

这应该是一个总结,我认为它可以帮助任何人有相关的问题。

如何将 Linux 资源表备份到 M4 SRAM 并在 A53重新启动时将其恢复?

步骤0:确保启用了 M4"部分"MCU 隔离、然后您可以从 MCUSS 向 A53发出热复位命令

关键参数如下所示

(1) pscMain2MCUDiable = 1;

(2) pscMCU2MainDiable = 0;

(3) PSMCU2DMDisable = 0;

(4) SOC_enableReset隔离(pscMain2MCUDiable、pscMCU2MainDiable、PSMCU2DMDisable、debugIsolationEnable)

(5) SOC_generateSwWarmResetMainDomainFromMcuDomain()重置主域。

步骤1:定义4KB 的存储器来存储 Linux 表

M4应用程序运行后、M4需要将"linuxResourceTable"从 DDR 备份到内部 SRAM、您需要定义一个特殊存储器区域(SRAM)来存储它。

(1)修改 M4项目代码中的 link.cmd

步骤2:将 DDR 地址空间转换为"本地存储器视图(M4)"

(1) RAT:让 M4内核映射 DDR 内存区域、并访问 DDR 中的 linuxResourceTable。

(2) MPU:添加 MPU 区域以允许从 DDR 执行 M4内核

步骤3:将 DDR 内容移动到 M4F 内核

(1) memcpy (&linuxResourceTable_back、localAddr、sizeof (linuxResourceTable_back))

步骤4:将 M4F DRAM 存储器移动到 DDR

A53复位(从 MCUSS 获得热复位)后、我们使用 R5 DM 将"linuxResourceTabl"从 M4 SRAM 恢复到 DDR

因为当主域(A53)重新启动时、R5 DM 必须重新加载

(1) R5示例代码"ipc_rpmsg_echo"已经包含 sciserver init (DM)、因此我们可以重新编译和修改此示例、并替换预编译的 R5 FW

(2) memcpy (0x05040000、0x9CC00000、0x1000)、将 M4 SRAM (linuxResourceTable)复制 到 DDR

如果有任何问题、请纠正我。

谢谢

Gibbs

嗨、Gibbs、

我认为你上面所说的是正确的。

但我还有一个问题:

(1) R5示例代码"ipc_rpmsg_echo"已包含 sciserver init (DM)、因此我们可以重新编译和修改此示例、并替换预编译的 R5 fw

@Anil

最后、从 Linux 内核加载 DM R5F 更新二进制文件。

由于我之前从未烧录 R5代码、因此如何推送生成的代码 .out 中 bin 才能使其在我修改 R5代码后正常工作?

此致、

Devin。

您好、Gibbs、

上述步骤正确。

@Devin、请按照以下步骤操作。 这里的步骤属于 CDD_IPC 集成、相同的过程也适用于您的用例。

首先、您需要在版本编译中编译上述 IPC 示例、然后将获得.out 文件。

稍后、从下面的链接、您可以按照从5到12的步骤操作。

请告诉我,如果你卡在任何地方.

此致、

Anil.

出于功能安全考虑、客户不会(持续)对不同的域复位使用部分隔离。

[/报价]你好、Gibbs、

用户希望使用 IPC 通信。

在 IPC 中、使用的共享存储器是 DDR、它位于主域中。 因此、当需要 IPC 时、唯一可行的选择是使用部分隔离。 在此配置中、MCU 域可以访问主域外设和存储器。

但是、如果这种方法违反了用户的安全要求、则不建议继续执行。

我即将结束该主题。 如有任何进一步的疑问、请打开新主题。

此致、

Anil.