工具/软件:

我在更新 CCS 版本时遇到 Java 错误。 创建案例后、我将附加屏幕截图、因为 现在没有选项。

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

工具/软件:

我在更新 CCS 版本时遇到 Java 错误。 创建案例后、我将附加屏幕截图、因为 现在没有选项。

尊敬的 Chandran:

您看到的更新错误是影响某些 Windows 环境(https://sir.ext.ti.com/jira/browse/EXT_EP-12157)的已知问题。 我们正在考虑在本周发布一份应该解决此问题的更新。

谢谢、

Ricky

CCS v20.1.1的更新包尚不可用、但正在按计划在周末发布。 20.1.1的脱机桌面安装可在 TI.com 上的以下位置获取: https://www.ti.com/tool/download/CCSTUDIO

谢谢、

Ricky

Patrick Chuong 非常感谢昨天的简短通话。 我跟踪了存储器范围重叠、发现存储器仅定义一次(例如 linker.cmd 文件中的 OCMC_RAM1 (RMX))。 但是、在某个编译工具引用它两次、这表明这是一个错误。 此外、也没有存储器溢出。 请参阅上面我的观点所附的屏幕截图。

Patrick 您好、非常感谢今天上午的通话以及对 CCS 10和20进行编译。 我测量了复位引脚、这样就可以了。 但我仍然收到这个错误消息。 有什么提示? 我看到许多用户在您的技术支持论坛上遇到了相同的问题: 设备处于重置状态。 使器件退出复位状态、然后重试此操作。 -处理器论坛-处理器- TI E2E 支持论坛

CortexA15_0:GEL 输出:-->>AM572x Cortex A15启动序列正在进行中... <<<--

CortexA15_0:GEL 输出:--> AM572x Cortex A15启动序列完成! <<<--

C66xx_DSP2:连接到目标时出错:(错误-1180 @ 0x0)器件保持在复位状态。 使器件退出复位状态、然后重试此操作。 (仿真包9.4.0.00129)

尊敬的 Chandran:

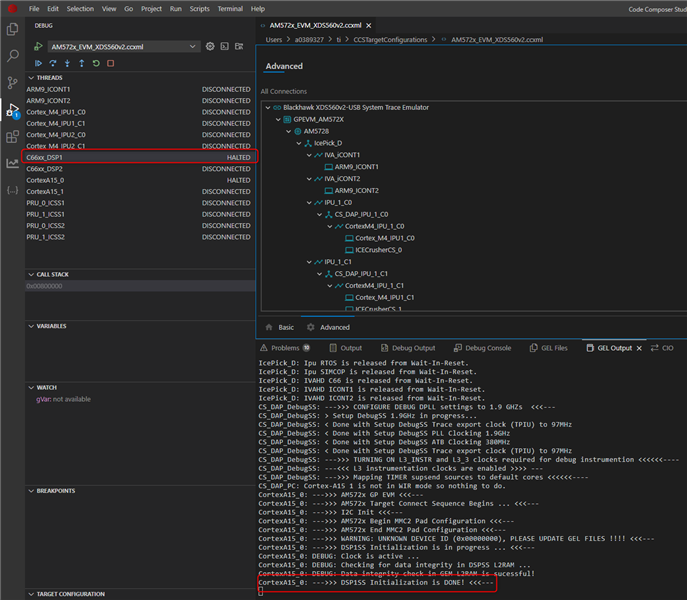

我尚未使用 CCS 20、因此不确定我是否可以根据需要帮助 CCS、但内核保持复位状态、因为您必须先初始化内核、然后才能加载任何内容。

这是过去通过 GEL 文件完成的、我假设它们被用作屏幕截图所示的用途。 下一步是使用脚本启用内核。

请参阅以下取自 CCS (Eclipse)的注释

Cortex_M4_IPU1_C0: GEL Output: --->>> AM571x Cortex M4 Startup Sequence In Progress... <<<--- Cortex_M4_IPU1_C0: GEL Output: --->>> AM571x Cortex M4 Startup Sequence DONE! <<<--- Cortex_M4_IPU1_C1: GEL Output: --->>> AM571x Cortex M4 Startup Sequence In Progress... <<<--- Cortex_M4_IPU1_C1: GEL Output: --->>> AM571x Cortex M4 Startup Sequence DONE! <<<--- C66xx_DSP: GEL Output: --->>> AM571x C66x DSP Startup Sequence In Progress... <<<--- C66xx_DSP: GEL Output: --->>> AM571x C66x DSP Startup Sequence DONE! <<<--- CortexA15_0: GEL Output: --->>> AM571x Cortex A15 Startup Sequence In Progress... <<<--- CortexA15_0: GEL Output: --->>> AM571x Cortex A15 Startup Sequence DONE! <<<--- At this point you only connected to the device.. now one connects to the a15 core: IcePick_D: GEL Output: Ipu RTOS is released from Wait-In-Reset. IcePick_D: GEL Output: Ipu SIMCOP is released from Wait-In-Reset. IcePick_D: GEL Output: IVAHD C66 is released from Wait-In-Reset. IcePick_D: GEL Output: IVAHD ICONT1 is released from Wait-In-Reset. IcePick_D: GEL Output: IVAHD ICONT2 is released from Wait-In-Reset. CS_DAP_DebugSS: GEL Output: --->>> CONFIGURE DEBUG DPLL settings to 1.9 GHZs <<<--- CS_DAP_DebugSS: GEL Output: > Setup DebugSS 1.9GHz in progress... CS_DAP_DebugSS: GEL Output: < Done with Setup DebugSS Trace export clock (TPIU) to 97MHz CS_DAP_DebugSS: GEL Output: < Done with Setup DebugSS PLL Clocking 1.9GHz CS_DAP_DebugSS: GEL Output: < Done with Setup DebugSS ATB Clocking 380MHz CS_DAP_DebugSS: GEL Output: < Done with Setup DebugSS Trace export clock (TPIU) to 97MHz CS_DAP_DebugSS: GEL Output: --->>> TURNING ON L3_INSTR and L3_3 clocks required for debug instrumention <<<<<<---- CS_DAP_DebugSS: GEL Output: ---<<< L3 instrumentation clocks are enabled >>>> --- CS_DAP_DebugSS: GEL Output: --->>> Mapping TIMER supsend sources to default cores <<<<<<---- CS_DAP_PC: GEL Output: Cortex-A15 1 is not in WIR mode so nothing to do. CortexA15_0: GEL Output: --->>> AM571x Target Connect Sequence Begins ... <<<--- CortexA15_0: GEL Output: --->>> AM571x PG2.0 GP device <<<--- CortexA15_0: GEL Output: --->>> PRCM Clock Configuration for OPPNOM in progress... <<<--- CortexA15_0: GEL Output: Cortex A15 DPLL OPP 0 clock config is in progress... CortexA15_0: GEL Output: Cortex A15 DPLL is already locked, now unlocking... CortexA15_0: GEL Output: Cortex A15 DPLL OPP 0 is DONE! CortexA15_0: GEL Output: IVA DPLL OPP 0 clock config is in progress... CortexA15_0: GEL Output: IVA DPLL OPP 0 is DONE! CortexA15_0: GEL Output: PER DPLL OPP 0 clock config in progress... CortexA15_0: GEL Output: PER DPLL already locked, now unlocking CortexA15_0: GEL Output: PER DPLL OPP 0 is DONE! CortexA15_0: GEL Output: CORE DPLL OPP 0 clock config is in progress... CortexA15_0: GEL Output: CORE DPLL OPP already locked, now unlocking.... CortexA15_0: GEL Output: CORE DPLL OPP 0 is DONE! CortexA15_0: GEL Output: ABE DPLL OPP 0 clock config in progress... CortexA15_0: GEL Output: ABE DPLL OPP 0 is DONE! CortexA15_0: GEL Output: GMAC DPLL OPP 0 clock config is in progress... CortexA15_0: GEL Output: GMAC DPLL OPP 0 is DONE! CortexA15_0: GEL Output: GPU DPLL OPP 0 clock config is in progress... CortexA15_0: GEL Output: GPU DPLL OPP 0 is DONE! CortexA15_0: GEL Output: DSP DPLL OPP 0 clock config is in progress... CortexA15_0: GEL Output: DSP DPLL OPP 0 is DONE! CortexA15_0: GEL Output: PCIE_REF DPLL OPP 0 clock config is in progress... CortexA15_0: GEL Output: PCIE_REF DPLL OPP 0 is DONE! CortexA15_0: GEL Output: --->>> PRCM Clock Configuration for OPP 0 is DONE! <<<--- CortexA15_0: GEL Output: --->>> PRCM Configuration for all modules in progress... <<<--- CortexA15_0: GEL Output: --->>> PRCM Configuration for all modules is DONE! <<<--- CortexA15_0: GEL Output: --->>> DDR3 Initialization is in progress ... <<<--- CortexA15_0: GEL Output: DDR DPLL clock config for 666MHz is in progress... CortexA15_0: GEL Output: DDR DPLL clock config for 666MHz is in DONE! CortexA15_0: GEL Output: Launch full leveling CortexA15_0: GEL Output: Updating slave ratios in PHY_STATUSx registers CortexA15_0: GEL Output: as per HW leveling output CortexA15_0: GEL Output: HW leveling is now disabled. Using slave ratios from CortexA15_0: GEL Output: PHY_STATUSx registers CortexA15_0: GEL Output: --->>> DDR3 Initialization is DONE! <<<--- CortexA15_0: GEL Output: --->>> Mapping TIMER supsend sources to default cores <<<<<<---- CortexA15_0: GEL Output: --->>> IPU1SS Initialization is in progress ... <<<--- CortexA15_0: GEL Output: --->>> IPU1SS Initialization is DONE! <<<--- CortexA15_0: GEL Output: --->>> IPU2SS Initialization is in progress ... <<<--- CortexA15_0: GEL Output: --->>> IPU2SS Initialization is DONE! <<<--- CortexA15_0: GEL Output: --->>> DSP1SS Initialization is in progress ... <<<--- CortexA15_0: GEL Output: DEBUG: Clock is active ... CortexA15_0: GEL Output: DEBUG: Checking for data integrity in DSPSS L2RAM ... CortexA15_0: GEL Output: DEBUG: Data integrity check in GEM L2RAM is sucessful! CortexA15_0: GEL Output: --->>> DSP1SS Initialization is DONE! <<<--- CortexA15_0: GEL Output: --->>> IVAHD Initialization is in progress ... <<<--- CortexA15_0: GEL Output: DEBUG: Clock is active ... CortexA15_0: GEL Output: --->>> IVAHD Initialization is DONE! ... <<<--- CortexA15_0: GEL Output: --->>> PRUSS 1 and 2 Initialization is in progress ... <<<--- CortexA15_0: GEL Output: --->>> PRUSS 1 and 2 Initialization is in complete ... <<<--- CortexA15_0: GEL Output: --->>> AM571x Target Connect Sequence DONE !!!!! <<<--- Then find the menu above that has Scripts-->AM57x_MULTICORE Initialization-->DSPSSClkEnable_API Should look like this: GEL Output: --->>> DSP1SS Initialization is in progress ... <<<--- CortexA15_0: GEL Output: DEBUG: Clock is active ... CortexA15_0: GEL Output: DEBUG: Checking for data integrity in DSPSS L2RAM ... CortexA15_0: GEL Output: DEBUG: Data integrity check in GEM L2RAM is sucessful! CortexA15_0: GEL Output: --->>> DSP1SS Initialization is DONE! <<<---

Chandran、

这毫无意义...

我的问题是、为什么现在? 这上周有效...也许一些 GEL 文件(无论它们是什么、做什么)在清理和迁移期间被删除了? I [/报价]在您的设置中、某个器件会使内核解除复位状态、但这并不只是发生。 请注意工作场景中遵循的确切程序。

CCS 20.x 尚未正式用于测试 AM57、因此我没有相关经验、因此在这方面我没有太多帮助。 请阅读 CCS 版本随附的文档。

-Josue

这不是硬件问题、并且器件未处于复位状态。 因为、测试连接对所有内核都是干净的。 请在下面查看良好的结果:

Chandran、

请分享您的确切程序

请参阅以下文档: software-dl.ti.com/.../AM572x_GP_EVM_、Hardware_Setup

-Josue

Chandran、

您的日志显示您的设备处于重置状态。

C66xx_DSP2:连接到目标时出错:(错误-1180 @ 0x0)器件保持复位状态。 使器件退出复位状态、然后重试此操作。 (仿真包9.4.0.00129)

我在上面分享的文档说明了如何在随附的视频中执行以下操作:

e2e.ti.com/.../CCS_5F00_c66x_5F00_core_5F00_out_5F00_of_5F00_reset.mp4

此致、

Josue

您的同事 Patrick 已尝试过相同的流程、但问题未解决。 还包括 Reset 是一条虚假的错误消息-电路板中没有物理复位、我之前说过这一点。 我们需要确保正确执行 GEL 文件。 如果你有信心解决这个问题,你需要拿起电话,现在打电话给我,停止这不必要的无用追逐鬼. 我别无选择、只能通过我们的首席执行官升级到您的高级首席执行官、因为我们期望作为一个普通客户、能够获得更好、更快速的解决方案。 由于技术支持不佳、我们还决定将哪种微型设备用于我们未来的产品。

很抱歉、我还没有收到任何会议邀请。 我刚刚刷新了收件箱。 下面是我设置的、我们也可以使用。

________________________________________________________________________

Microsoft Teams 需要帮助?

会议 ID:291 439 458 564 2.

密码:iA7Dy7fZ

通过电话拨入

+1 872-212-4,377,362090521# United States, Chicago

+506 4102 3,318,362090521# Costa Rica、所有地点

+44 20 3443 9384,,362090521#英国,伦敦市

+40 21 529 2,063,362090521# Romania、Bucharest

+91 22 6001 1904、、、362090521#印度、孟买

+63 2 8231 3,217,362090521# Philippines、Manila

电话会议 ID:362 090 521#

____________________________________________________________________

此致、

Chandran Palanisamy |高级电气工程师(基于模型的开发)|布兰森焊接和组装

艾默生自动化解决方案 | 46280 Dylan Dr #100 | Novi, MI 48377, USA.

+1 (248) 797-9758.

Chandran、

根据我们的在线会议、我发现问题是核心没有初始化。

帮助您设置目标配置后、我们确认您能够连接内核。

我认为这一主题已解决。 请记住、AM57x 目前不支持 CCS20。

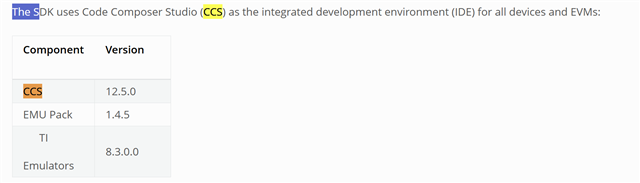

有关受支持的 CCS 版本、请参阅 SDK 发行说明

https://software-dl.ti.com/processor-sdk-rtos/esd/AM57X/09_03_00_00/exports/docs/devices/AM57X/rtos/Release_Specific_Release_Notes.html

此致、

-Josue

请记住、AM57x 目前不支持 CCS20。

简而言之、CCS 20在技术上确实支持 AM57x。 我能够创建配置并启动 AM572x EVM 配置的调试会话、连接到 A15、然后使用 GEL 热菜单使 DSP 退出复位状态、然后连接到 DSP。

因此、虽然可以使用 CCS 20进行调试、但设备团队是否建议(支持)也是另一个故事。

谢谢

Ki