工具/软件:

我们迫切需要澄清!

LPDDR4配置设置查询。

我们向 Micron 发送了一个装有 MT53E256M32D1KS-046 AAT:L 的丰田 PWB 以进行 LPDDR4测试、并提供了包含附加 DDR 配置的 SW 映像、其结果如下:

1.培训总结:

1A。 写入水平:MR2第7位未设置->未应答。 请说明需要做什么。

1b。 在初始化和正常操作期间没有观察到 MR4读取命令->根据 TI 的响应、我们知道它将在未来的 SDK 版本中进行规划。 将在哪个 SDK 版本中处理此功能?

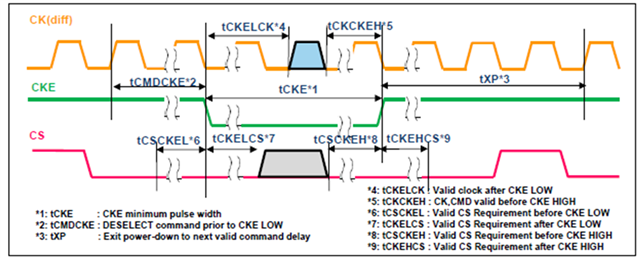

由于 CKE 始终为高电平、因此无法对 tCKCKEH、tCKELCK、tCMDCKE 和 TxP 执行测量

3、自刷新:

tREFIpb 和 tPBR2PBR:未观察到刷新 PB 命令

TSR、tXSR 和 tESCKE:未观察到自刷新命令

此致、

Vishwajit V K