工具/软件:

这是 TI 文档、不提供 OSPI 开关特性-数据传输。

您能否提供涵盖要求和开关特性的交流规格?

谢谢

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

工具/软件:

这是 TI 文档、不提供 OSPI 开关特性-数据传输。

您能否提供涵盖要求和开关特性的交流规格?

谢谢

您好、Max、

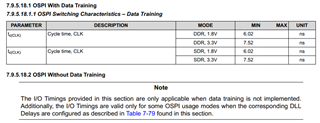

表6-107 OSPI 开关特性–PHY 数据处理请参阅 图6-90 和 图6-91

|

编号 |

参数 |

|

消耗量 |

最小值 |

最大值 |

人员 |

|

O1. |

tc (CLK) |

周期时间、OSPI0/1_CLK |

1.8V、DDR |

6.0 |

6.0 |

ns |

|

O7. |

|

|

1.8V、SDR |

6.0 |

6.0 |

ns |

|

O2 |

tw (CLKL) |

脉冲持续时间、OSPI0/1_CLK 低电平 |

DDR |

(0.475P (1)- 0.3) |

|

ns |

|

O8. |

|

|

特别提款权 |

|

|

|

|

O3. |

tw (CLKh) |

脉冲持续时间、OSPI0/1_CLK 高电平 |

DDR |

(0.475P (1)- 0.3) |

|

ns |

|

O9. |

|

|

特别提款权 |

|

|

|

|

O4. |

td (CSN-CLK) |

延迟时间、OSPI0/1_CSn[3:0]有效边沿到 OSPI0/1_CLK 上升沿 |

DDR |

ns |

||

|

O10. |

|

|

特别提款权 |

|

|

|

|

O5. |

td (CLK-CSn) |

延迟时间、OSPI0/1_CLK 上升沿到 OSPI0/1_CSn[3:0]无效边沿 |

DDR |

ns |

||

|

O11. |

|

|

特别提款权 |

|

|

|

|

O6. |

td (CLK-D) |

延迟时间、OSPI0/1_CLK 有效边沿到 OSPI0/1_D[7:0]转换 |

DDR |

ns |

||

|

O12 |

|

|

特别提款权 |

|

|

|

|

tDIVW |

(O6最大值-最小值) |

DDR |

|

1. |

ns |

|

|

|

|

(O12最大值-最小值) |

特别提款权 |

|

|

|

(1) P = SCLK 周期时间(以 ns 为单位)= OSPI0/1_CLK 周期时间(以 ns 为单位)

(2) M = OSPI_DEV_DELAY_REG[D_INIT_FLD]

(3) N = OSPI_DEV_DELAY_REG[D_AFTER_FLD]

(4) R =基准时钟周期时间(以 ns 为单位)

(5) TD = PHY_CONFIG_TX_DLL_DELAY_FLD

(6) 当使用数据训练查找合适的数据有效窗口时、未定义 OSPI0/1_D[7:0]输出的最小和最大延迟时间。 tDIVW 参数定义了最大数据无效窗口。 提供此参数来代替最小和最大延迟时间、必须使用它来检查与所连接器件的数据有效窗口要求的兼容性。

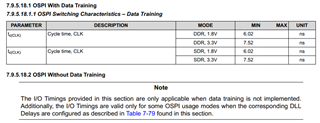

这些将在数据表的最新修订版本中进行更新。 现在、我在这里附上了时序要求和开关特性。

此致、

马特