Thread 中讨论的其他器件:DRA829V、 TDA4VM

工具/软件:

您好、

我对插槽 PCIe0 (4通道1)上的 PCIe 时钟配置有疑问。

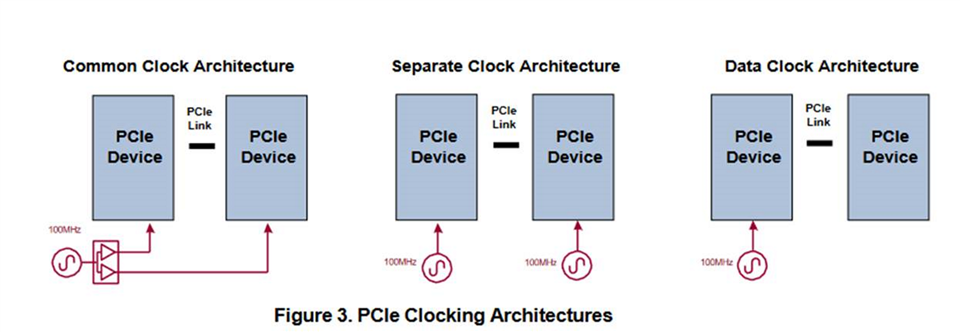

在电路板原理图上、PCIe 插槽的时钟由外部时钟发生器生成、相同的时钟进入 Jacinto 的 SERDES_REF_CLK 引脚。

我们使用 Jacinto 作为 RC、使用 Xilinx FPG A 板作为 EP、我希望这两个板都保持同步、但在我们的测试过程中、我不确定会是哪种情况、因为性能不如预期、所以我们研究了原因。

我找到这篇文章[常见问题解答] TDA4VM:TDA4VM/DRA829V:从外部路由 PCIe 参考时钟 =>"也向 TDA4VM SOC 提供了相同的 REFCLK、但 SDK 软件不使用此时钟源、而是为每个 PCIe SERDES 使用内部 PLL 时钟源"

因此、为了在 Jacinto 和 FPGA 之间实现同步 PCIe 时钟、我们只需修改 SDK 中的配置、而不修改电路板上的硬件?

您能告诉我们必须在 SDK 中修改什么才能正确设置它吗、我们使用的是 SDK 09_00_00_02

此致

Mickael