工具/软件:

您好、

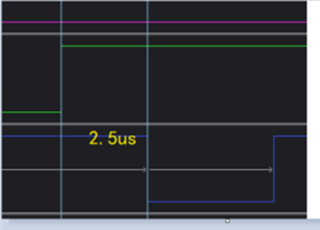

我使用 SDK 8.6版、通过 A53引导 R5F、并涉及 IPC (处理器间通信)。 在运行期间、我发现从检测到硬件 IO 端口的变化到开始进入中断处理功能的延迟时间不稳定。 有时延迟超过500纳秒、有时会达到1微秒、甚至达到2微秒。 我使用逻辑分析仪并通过在中断进入功能中切换 IO 引脚电平来测量此情况。 当 R5F 内核在 DDR 上运行时、会发生这种情况。 当我不使用 A53引导 R5F、而是从 MSRAM 运行整个程序时、测量结果也不稳定。 我对这部分感到很困惑。 您能帮助分析一下吗? 即使在此过程中执行堆栈操作、是否会发生如此大的延迟? 值得注意的是、我正在使用的外部中断的优先级设置为0、这应该是最高优先级。

绿色(信号)的上升沿是硬件外部中断到达的实际时刻、蓝色(信号)的下降沿是刚刚进入中断处理函数的时刻。

整个方案包括三项任务:

- UART 数据处理任务 :

- 优先事项:30

- UART 使用中断驱动的接收、中断优先级为4。

- SPI 无线模块通信任务 :

- 优先事项:33

- 仅每2秒处理一次、使用轮询模式进行 SPI 通信。

- LED 控制任务 :

- 优先事项:25

此配置在实时响应能力(例如 UART 处理高优先级中断)与周期性后台任务(SPI)和低优先级视觉反馈(LED 控制)之间实现了平衡。

很高兴收到您的消息!