请注意,本文内容源自机器翻译,可能存在语法或其它翻译错误,仅供参考。如需获取准确内容,请参阅链接中的英语原文或自行翻译。

器件型号:TDA4VE-Q1 工具/软件:

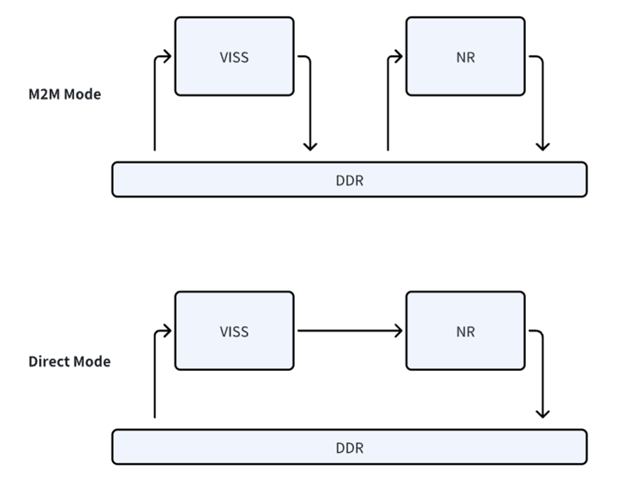

当前的 VPAC Fvid2驱动程序都带有 M2M 前缀、这意味着它们仅支持存储器到存储器操作(如果我正确)。 在某些情况下、我们可以通过硬连线或本地缓存直接连接两个模块(如 VISS 和 NR)、并绕过 DDR 操作、这将消耗更少的 DDR 带宽并具有更低的端到端延迟。 我认为 HTS (硬件线程调度器)是要执行此操作的吗? 但 TRM 中似乎缺少"HTS 部分"。 是否有示例展示了如何 在不使用 DDR 的情况下直接连接模块(图片中的"直接模式")?