工具/软件:

尊敬的专家:

通知 J784S4 E5 J742S2 E2 EVM 系统更新 v1.0.pdf

GPIO 8是 EN_GRP_PDN 类型、 它将在上电序列的3ms 阶跃之前锁存。

我想知道3mS 从什么时候到什么时候?

当我将其连接到 VSYS_mcuio_3V3、时、似乎锁存为0 (I 测试降压稳压器5的输出)

当我将其连接到 VSYS_IO_3V3时、似乎锁存1 I 测试降压5的输出);

我对 结果感到困惑;

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

工具/软件:

尊敬的专家:

通知 J784S4 E5 J742S2 E2 EVM 系统更新 v1.0.pdf

GPIO 8是 EN_GRP_PDN 类型、 它将在上电序列的3ms 阶跃之前锁存。

我想知道3mS 从什么时候到什么时候?

当我将其连接到 VSYS_mcuio_3V3、时、似乎锁存为0 (I 测试降压稳压器5的输出)

当我将其连接到 VSYS_IO_3V3时、似乎锁存1 I 测试降压5的输出);

我对 结果感到困惑;

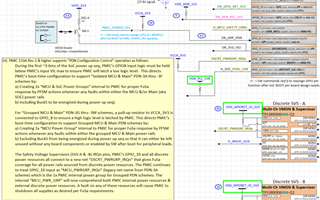

GPIO8的锁存时间为 EN_3V3_VIO 控制信号置位后3ms (源自 GPIO9)。 这是 PMIC 状态机开始执行 SoC 上电序列所置为有效的第一个信号。

GPIO8应上拉至 VSYS_3V3或 VCCA_3V3电源轨、因为这些电源将稳定、并且不包含在 SoC 上电序列中。 请参阅以下快照摘自"PDN-3G 方案"(分组 MCU 和主 PDN 类型)、后者是详细"J784S4 EVM 单 Leo 双 HCP PDN-3AFGM v0.31"图的一部分(如下所示)。

e2e.ti.com/.../J784S4-EVM-Single-Leo-Dual-HCPS-PDN_2D00_3AFGM-v0.31.pdf

关注:

我使用的是 PDN-3F、 GPIO-8引脚应该连接到哪里?

在 proc141E4:它上拉至 VSYS_MCUIO_3V3 NVM 2

在 PROC141E5:它上拉至 VCCA_3V3、但与 PROC141E5 第31页上的 VDA_DLL_0V8相反

我想我会使用降压5为 VDD_MCU_0V85供电,并且 GPIO8应该被锁存为0 ,是这样吗?

其他问题:

对于我的实验:3ms 从 EN_VIO_3V3开始, VSYS_MCUIO_3V3‘s 输出也是第一个电源,它在3mS 之前关闭了 Latech 1 ,但它锁存0 ,似乎接线?