Thread 中讨论的其他器件:TDA4VH

工具/软件:

3.3V -> 1.8V ->低电压内核->低电压 RAM 的上电时序的时序要求是什么?

SPRSP79B 处理器规范中的表6.10.2.2是否显示了最低时间要求、或者它只是显示了在其参考设计中对 TDA4VH 加电时发生的时序?

例如、一旦3.3V 电压上升、1.8V 电压能否立即开始斜升、或者是否有某些原因导致电压需要在特定的时间窗口内相互斜升?

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

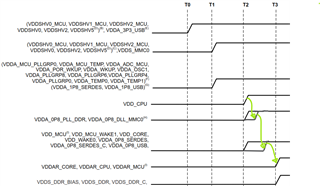

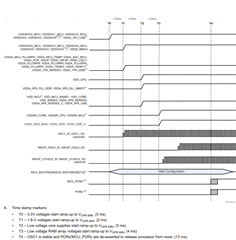

不同输入电源(3.3V -> 1.8V ->低电压内核->低电压 RAM)的上电时序要求是每个输入电源在 Seq 中的下一个电源开始斜升之前达到最小工作电压(Vopr min)。 TDA4VH DM 的第6.10.2节中每个时间阶跃显示的经过时间周期反映了使用建议的 PDN-3A 实现(考虑了温度和生产批次范围内电源元件的最小到最大延迟)时的 J784S4 EVM 设计性能。

感谢您的回答。

作为对此的后续跟进、

对于 SoC 上电、为了实现运行或可靠性、是否所有0.8V 电源轨都不会同时开始斜升并大致同时完成斜升很重要?

相反、例如此处、如果0.8V 电源一个接一个地定序、但前提是最后一个0.8V 电源在下一个0.85V 和1.1V 电源开始斜升之前仍将达到其工作电压电平?

(您可以考虑相同问题适用于任何或所有电源轨、但我这里仅使用0.8V 电源作为示例。)