请注意,本文内容源自机器翻译,可能存在语法或其它翻译错误,仅供参考。如需获取准确内容,请参阅链接中的英语原文或自行翻译。

器件型号:TDA4VEN-Q1 工具/软件:

你(们)好

请告诉我们 TDA4VEN-Q1的目标阻抗(Z11)。

我想知道所有电源网的目标阻抗、如果没有、

请告诉我一些需要特别考虑的电源(例如 LPDDR4、MIPI、OLDI)。

此致、

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

工具/软件:

你(们)好

请告诉我们 TDA4VEN-Q1的目标阻抗(Z11)。

我想知道所有电源网的目标阻抗、如果没有、

请告诉我一些需要特别考虑的电源(例如 LPDDR4、MIPI、OLDI)。

此致、

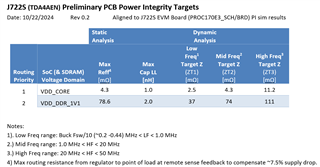

TDA4VEN/AEN (J722S) SoC 对于 VDD_CORE 和 VDD_DDR_1V1输入电源有2个目标阻抗、如下所示。

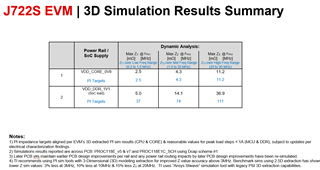

下面显示了 EVM PCB 和 DCAP 方案的 J722S EVM 电源完整性3D 仿真结果与 PI 目标的关系。

由于负载阶跃、没有其他 SoC 输入电源具有 PI Z 目标。 所有其他低负载数字和模拟输入电源应遵循良好的 PCB 和电源设计实践、以实现:

1. PCB 布线 IR 压降<电源电压电平的1%

2.输入电源噪声幅值(所有类型)<+/-25mVpp