主题:SysConfig 中讨论的其他器件

工具/软件:

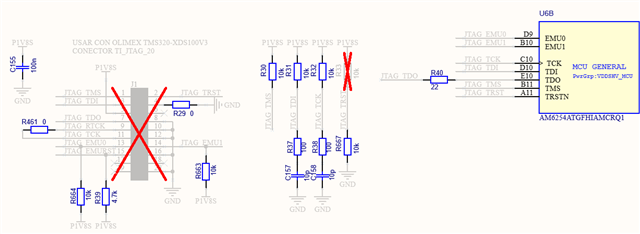

我们开发了基于 AM6254ATGFHI 的定制电路板、具有使用 ISSI IS43LQ16512A-053BLI 器件的 LPDDR4存储器接口。 各种元件的所有电源轨均已正确供电、并且系统复位信号已正确生成。 我们能够从 SD 卡启动 U-Boot 而不会出现问题。

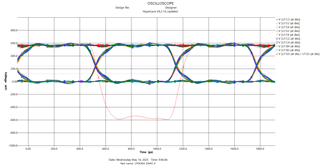

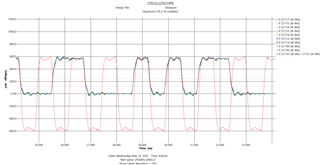

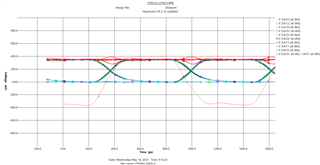

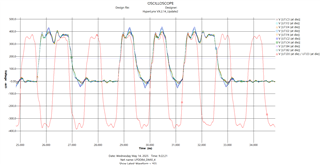

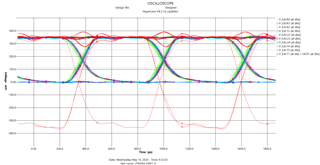

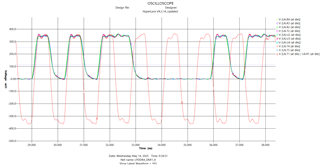

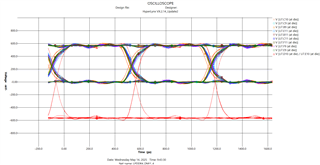

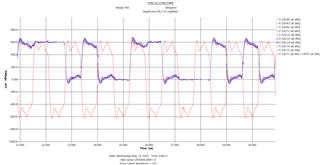

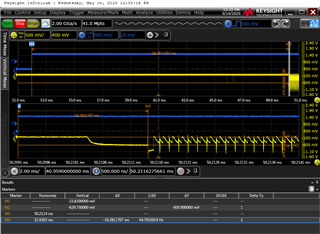

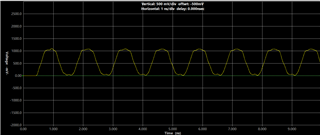

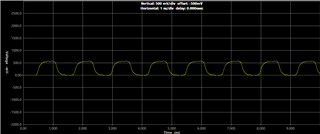

使用 HyperLynx 对 LPDDR4存储器接口进行了仿真、并成功传递了"DDRx 批处理仿真"。

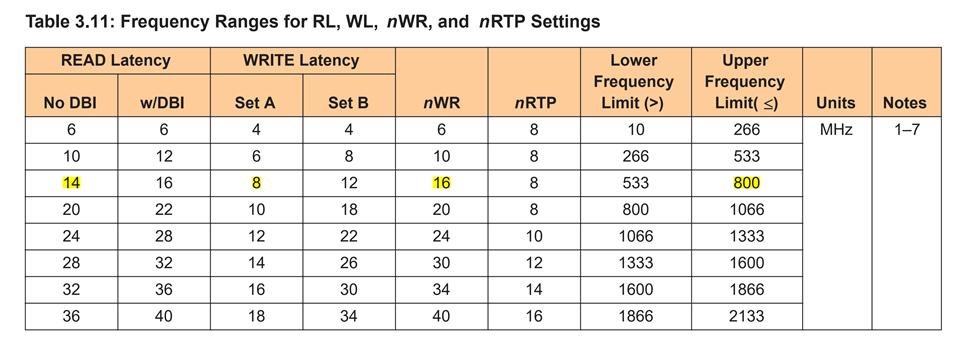

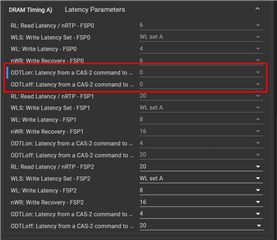

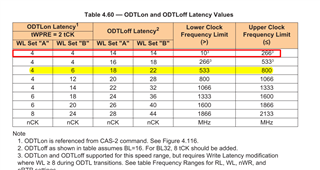

为了生成 U-Boot 配置文件、我们使用 TI SysConfig 工具根据存储器器件数据表中提供的信息和信号完整性仿真的输出创建 DTSI 文件。

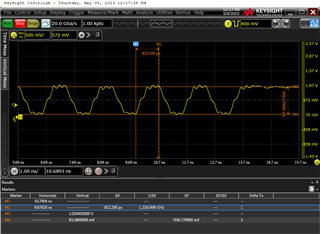

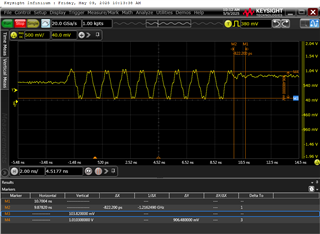

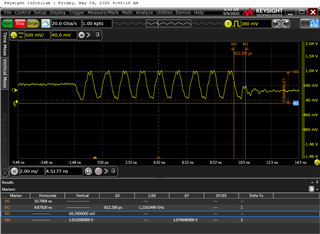

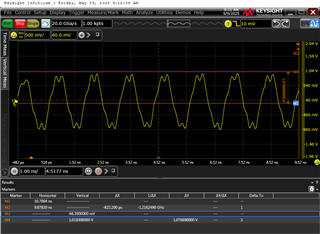

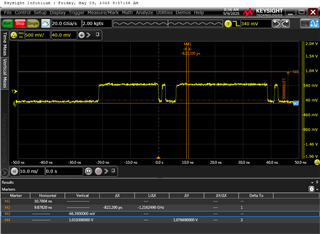

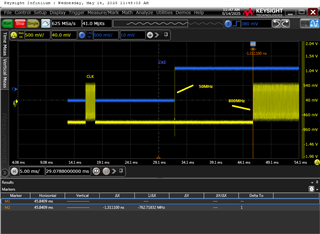

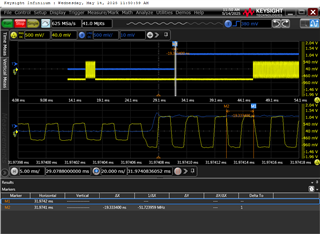

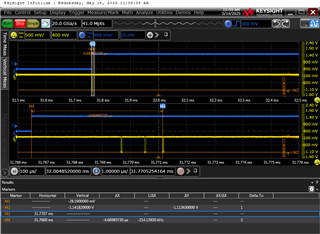

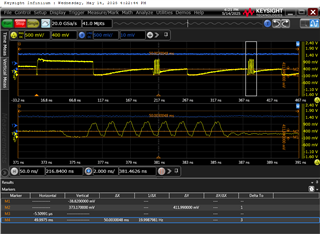

但是、在启动电路板并运行存储器测试时、我们会观察到频繁的读取/写入错误、其中数据显示为全零、而不是预期值。

您能否就我们可能做得不正确提供任何指导?

最好的 regards.e2e.ti.com/.../report_5F00_data.zipe2e.ti.com/.../settings_5F00_info_5F00_2505071627.zipe2e.ti.com/.../Serial-output-UART0.txt