工具/软件:

尊敬的专家

我尝试调试一些 eMMC 问题、并尝试降低 eMMC 速度。

相关主题如下所示。

我是否可以知道如何在 u-boot/linux 中修改 dts?

如果 "仅限传统模式"、此代码是否正确?

sdhci0: mmc@fa10000 {

compatible = "ti,am62-sdhci";

reg = <0x00 0x0fa10000 0x00 0x1000>, <0x00 0x0fa18000 0x00 0x400>;

interrupts = <GIC_SPI 133 IRQ_TYPE_LEVEL_HIGH>;

power-domains = <&k3_pds 57 TI_SCI_PD_EXCLUSIVE>;

clocks = <&k3_clks 57 5>, <&k3_clks 57 6>;

clock-names = "clk_ahb", "clk_xin";

assigned-clocks = <&k3_clks 57 6>;

assigned-clock-parents = <&k3_clks 57 8>;

bus-width = <8>;

/* mmc-ddr-1_8v; */

/* mmc-hs200-1_8v; */

ti,clkbuf-sel = <0x7>;

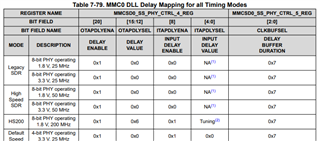

ti,otap-del-sel-legacy = <0x0>;

/delete-property/ ti,otap-del-sel-mmc-hs = <0x0>;

/delete-property/ti,otap-del-sel-ddr52 = <0x5>;

/delete-property/ ti,otap-del-sel-hs200 = <0x5>;

ti,itap-del-sel-legacy = <0xa>;

/delete-property/ ti,itap-del-sel-mmc-hs = <0x1>;

status = "ok";

};

如果 "ddr52 mode only"(仅限 ddr52模式)、则此代码是否正确?

我们仍然保持传统速度模式、对吧?

sdhci0: mmc@fa10000 {

compatible = "ti,am62-sdhci";

reg = <0x00 0x0fa10000 0x00 0x1000>, <0x00 0x0fa18000 0x00 0x400>;

interrupts = <GIC_SPI 133 IRQ_TYPE_LEVEL_HIGH>;

power-domains = <&k3_pds 57 TI_SCI_PD_EXCLUSIVE>;

clocks = <&k3_clks 57 5>, <&k3_clks 57 6>;

clock-names = "clk_ahb", "clk_xin";

assigned-clocks = <&k3_clks 57 6>;

assigned-clock-parents = <&k3_clks 57 8>;

bus-width = <8>;

/* mmc-ddr-1_8v; */

/* mmc-hs200-1_8v; */

ti,clkbuf-sel = <0x7>;

ti,otap-del-sel-legacy = <0x0>;

/delete-property/ ti,otap-del-sel-mmc-hs = <0x0>;

ti,otap-del-sel-ddr52 = <0x5>;

/delete-property/ ti,otap-del-sel-hs200 = <0x5>;

ti,itap-del-sel-legacy = <0xa>;

/delete-property/ ti,itap-del-sel-mmc-hs = <0x1>;

status = "ok";

};

如果引导成功、如何检查 eMMC 工作模式?

非常感谢

Gibbs