Thread 中讨论的其他器件:TDA4VH

工具/软件:

大家好、我介绍了这个主题: TDA4VH-Q1:在 SOC Jacinto -处理器论坛-处理器- TI E2E 支持论坛的 CPSW9g 开关内添加流控制

正如12月达成的协议、您是否设置了一项测试来让 Jacinto 生成暂停帧?

谢谢您、

此致、

Wissam

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

工具/软件:

大家好、我介绍了这个主题: TDA4VH-Q1:在 SOC Jacinto -处理器论坛-处理器- TI E2E 支持论坛的 CPSW9g 开关内添加流控制

正如12月达成的协议、您是否设置了一项测试来让 Jacinto 生成暂停帧?

谢谢您、

此致、

Wissam

您好、

soc 感谢您的更新。 没有问题,我们可以重新确认。

当然、您是否还可以通过在外部端口之间传输流量并将 CPU 保持在外部端口之一对等端的最大负载来进行检查。

此致、

Sudheer

您好、

当将 soc 保持在最大负载时、我们看到暂停帧由外部端口接收、但不传输到主机端口、似乎问题出在交换机级别

暂停帧将由外部端口本身接受、相同的帧不会传输到主机端口。

如果外部端口 fifo 已满、则 Hist 端口不会向其转发任何数据包、主机端口将向 UDMA 返回压力、并且不会接受来自应用程序的任何新数据包提交。

据我的理解、CPSW 没有看到任何 TX 暂停帧静态。

如上所述、当我们在外部正向连接中的两个 SOC 之间通信时、观察到从 CPSW 发送的暂停帧。

此致、

Sudheer

您好:

抱歉、我犯了个错误、您的理解是正确的、我们没有看到 CPSW 有任何 TX PAUSE 帧。

我对您的上述注释有疑问、您观察到从 Core A SOC A 向 Core B SOC B 发送数据时出现了暂停帧是否正确?

说到这里、您是指在同一 SOC 中的2个内核之间传输数据吗?

将数据传输到主机端口时不执行

谢谢您、

此致、

Wissam

您好、

关于您的上述评论、我有一个问题、您在将数据从 soc A 发送到 Core B SOC B 时观察到暂停帧是正确的吗?

是的、在两个 SOC 之间、即使用两个 TI EVM。

如果您这样说、您是指在同一个 soc 中的2个内核之间传输数据吗?

否、两个 SOC 之间。

此致、

Sudheer

您好、

确实、如果您在外部端口而不是主机端口上看到暂停帧、则意味着 soc 会发送暂停帧。 您能否与我分享统计数据、以了解我们应该期待什么、以及您所做的更改、以便我们可以重现这些变化?

是的、将共享统计信息和测试设置详细信息以及更改。

此致、

Sudheer

您好、

soc 您好、谢谢您、您打算通过什么方式与我们分享?

很抱歉延迟、因为硬件不可用性捕获日志已延迟。

将尝试在本周结束前提供设置图和 CPSW 统计信息。

此致、

Sudheer

您好:

感谢您的反馈,我有几个问题:

您说过"通过 PN_MAC_CTRL 寄存器的寄存器写入来启用/禁用流控制"。 我们在代码中激活了该寄存器(请参阅 https://e2e.ti.com/support/processors-group/processors/f/processors-forum/1382087/tda4vh-q1-adding-flow-control-inside-the-cpsw9g-switch-of-the-soc Jacinto /5374783#537478)、但它不起作用。 您能给我们提供您使用的测试代码吗?

您是否确认在2个10GbE CPSW 端口上也可以实现此流控制?

谢谢您、

此致、

Wissam

您好、

您是否确认接收数据(IP 地址为192.168.1.100)的 soc 内核是在 FreeRTOS 下将 LWIP 用作以太网栈的 R5F?

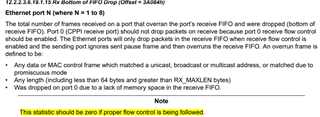

否、有关我的测试环境、请参阅下图。

在没有流控制的情况下:您说"在 soc 端口观察到 FIFO 上升值现象、在必须转发数据的其他外部端口观察到等效的数据包丢弃现象。" 。 您指的是哪个计数器?

端口3侧 rxTopOfDrop。

"rxTopOfFifoDrop = 1596"

端口5侧 Tx 丢弃。

txPriDrop[0] = 1596

txPriDropBcnt[0] = 2422728

In control flow enable cases:在 iperf 日志中、我们看到没有重试、并且并行、我们看到 rxBottomOfFifoDrops、这意味着帧在端口输入处丢失。这怎么可能(TRM 说:"如果流量控制正确、该统计数据应该为零?这里没有跌落、创建了一个方案、即在我的上述设置中、BottomOfFIFO 丢弃、MAC 端口3向 TDA4VH 发送暂停帧。

您可以观察到 Tx 暂停帧"txPauseFrames = 1544793"

因此、在看到暂停帧后、TDA4VH 将控制 Tx 流量、因此没有下降。Unknown 说:我们在代码中激活了该寄存器(请参阅 https://e2e.ti.com/support/processors-group/processors/f/processors-forum/1382087/tda4vh-q1-adding-flow-control-inside-the-cpsw9g-switch-of-the-soc Jacinto /5374783#537478)、但它不起作用。 您能否向我们提供您使用的测试代码?您也可以从 ETHFW 通过寄存器启用、如果您有疑问、请读取寄存器值并检查是否启用了流量控制?

[引述 userid="540868" url="~/support/processors-group/processors/f/processors-forum/1461157/tda4vh-q1-adding-flow-control-inside-the-cpsw9g-switch-of-the-user-jacinto/5677846#5677846"] soc 注意:

PN_MAC_CTRL 寄存器将保存 Tx 和 Rx 流控制使能的字段。 请同时启用两者。

我按原样使用 TI SDK、刚才已按照您之前介绍的内容启用了 CPSW 统计信息捕获功能。我还在 ETHFW 中禁用了 Monitor Task、因为它会在观察到底部 OfFIFO 下降时执行 CPSW 恢复。

如果 ETHFW 要检查流控制、我们需要禁用"ETHFW_MONITOR_SUPPORT"、如所示 否 来自 ETHFW 构建标志。[/quote]

请按照上面的说明进行检查。

此致、

Sudheer

您好:

感谢您提供测试设置的详细信息、现在更加清晰。

据我所知、您在尝试从一个外部端口与另一个外部端口通信时观察到了暂停帧。 我认为有一个误解,因为在我们方面,我们做了这样的测试:

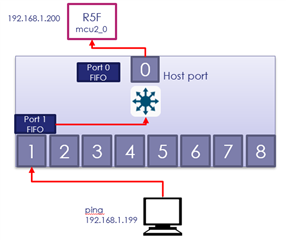

目标是能够在使用主机端口阻止 R5F 内核时生成暂停帧。 在我们这边、我们观察到主机端口仍然在传输数据、即使我们阻止了 R5F 内核。 我认为、通过使用2个外部端口、未使用端口0。

此外、我还有一个问题、FIFO 存储是否有开始发送暂停帧的阈值?

谢谢您、

此致、

Wissam

您好、

另外、我还有一个问题、soc 存储是否有开始发送暂停帧的阈值?

NI、我们没有针对 FIFO 阈值的任何特定配置。

[引述 userid="621619" url="~/support/processors-group/processors/f/processors-forum/1461157/tda4vh-q1-adding-flow-control-inside-the-cpsw9g-switch-of-the-user-jacinto/5686057#5686057"] soc。 我认为有一个误解,因为在我们方面,我们做了这样的测试:

目标是能够在使用主机端口阻止 R5F 内核时生成暂停帧。 在我们这边、我们观察到主机端口仍然在传输数据、即使我们阻止了 R5F 内核。 我认为、通过使用2个外部端口、未使用端口0。

[/报价]如果 R5F 被阻止、则不会有来自 R5F 的任何流量、如果启用了客户端、则客户端可以向 CPSW 发送流量。

我没有看到暂停帧与主机端口之间的暂停帧让我检查一次。

此致、

Sudheer

您好、

根据我们的理解、如果在阻止的同时从 PC 发送数据、端口0 soc 应该已满。 如果端口0 FIFO 已满、交换机本身应该发送暂停帧、这就是我们期望暂停帧的原因。

我想这是 FIFO 丢弃顶部位置。 让我在我这边检查一下、然后更新一下您的信息。

此致、

Sudheer

您好、

根据我们的理解、如果在阻止的同时从 PC 发送数据、端口0 soc 应该已满。 如果端口0 FIFO 已满、交换机本身应该发送暂停帧、这就是我们期望暂停帧的原因

我已经测试了上述情况、观察到外部端口始终将数据包转发到主机端口。

我没有观察到主机端口侧有任何下降、因为从外部端口发送的数据包将到达主机端口(而非 Rx FIFO)的 Tx FIFO 中、因此我们没有观察到暂停帧。

让我与 IP 团队核实、因为没有人从 Tx FIFO 读取数据、数据包在主机端口丢失。

此致、

Sudheer

您好、

让我与 IP 团队核实、因为没有人从 soc 读取数据、数据包在主机端口处丢失。 [/报价]是的、主机端口从外部端口接收流量时没有背压。

如果主机端口返回压力、它将阻止外部端口到外部端口的转发、则不应符合交换机的行为。

在这里、应用程序应负责较高层的流量处理、如 TCP。

当无法将流量转发到其他外部端口时、从外部端口启动暂停帧的唯一方法。

我们在上面已经确认了同样的情况。

如果您指定您的用例和最大流量、我们可以根据需要提供一些输入。

此致、

Sudheer

您好、

soc 这意味着外部端口之间的行为取决于主机端口。 您能否说明原因?

否、主机端口是独立的。 它不会影响外部端口到外部端口的转发、直到它有大量的数据包占用端口的整个带宽。

soc 如果主机端口背压阻止外部端口到外部端口的传输、则表示它 阻止了交换机的正常行为。

以上是将流量从外部端口转发到主机端口时流量控制不适用的原因之一。

基本上、您在 H/W 中询问 s/w 瓶颈(不是调度任务以使 DMA 从主机端口读取数据包)处理

如果在 s/w 交换机内部发生异常、则交换机将无法根据您的请求正常工作。

以上 不是任何开关的功能。 它将始终允许从外部端口切换流量。

soc 感谢您的提议。 就我们而言,这似乎是一个坏消息,因为使用 TCP 处理流量会降低我们的速度。

您的用例是什么、您的 s/w 是否未从主机端口读取数据?

此外、您的主机端口的吞吐率是多少、即内部消耗量和转发/交换流量。

交换 b/w 端口将以链路速率进行。

请从用例的角度分析所需的内容。

此致、

Sudheer

您好、

[引述 userid="621619" url="~/support/processors-group/processors/f/processors-forum/1461157/tda4vh-q1-adding-flow-control-inside-the-cpsw9g-switch-of-the-user-jacinto/5712081#5712081"] soc我们知道、要观察来自主机端口的暂停帧、应在端口本身达到最大带宽。

在本例中、我们需要从两个10G 外部端口读取主机端口、这就是我们认为暂停帧很有用的原因。 如果您有关于所支持带宽的信息、欢迎使用。

[/报价]偶数交换机支持接受20G 的两个端口。

R5F 或 A72等内部内核 和运行的 s/w 栈无法处理20G 的流量。

是否计划在 R5F 或 A72内核中以20Gbps 的数据处理运行?

此致、

Sudheer

您好、

我们计划将该20G 数据分发到多个内核上。 我们还计划做一些工作台来评估可能的情况。

20GB 也无法通过 TI SDK 软件实现。

您需要进行更多自定义设置、涉及所有内核、甚至 A72端还需要通过传递网络堆栈来进行数据交换、从而更改自定义驱动程序。

如果需要、任何 DSP 和深度学习应用都可以并行在 DSP 内核上运行。

此致、

Sudheer

您好、

本主题结束:

当 SoC 的内部内核(例如 R5F/A72)无法处理 在主机端口接收到的数据包时、暂停源自主机端口的帧、这不是预期行为。

这种情况 会导致 以下问题:

1)它阻止来自其他端口的流量 尝试到达 主机端口

2)它还阻止外部端口之间的转发。

因此、 只有 在 外部端口之间的流量转发过程中、并且仅在端口速度不匹配或由来自主机端口或其他外部端口的流量引起的拥塞情况下、才需要暂停帧。

这一点 已经得到确认、并已共享相关的 CPSW 统计信息以供参考。

如果由于 R5F 或 A72等内部内核上的加载、预计数据包丢失 为零、则应用程序必须通过软件实现适当的逻辑来进行流控制。

请告诉我们、在这一主题上是否需要任何进一步的协助。

此致、

Sudheer

您好:

非常感谢您总结本主题。

soc 否、请参阅下面的测试环境图。

正如 我们从您执行的测试中了解到的、暂停帧不会从目标端口发出、而是从转发数据的外部端口发出。 在测试中、端口3是转发数据、端口5是接收数据。 激活流量控制后、我们可以看到来自端口3的 Tx 暂停帧。

对于我们来说、暂停帧是从外部端口而不是从主机端口发回的、这是完全合适 的、我们看到端口3在尝试将数据转发到端口5 (外部端口)时会发回暂停帧。 在本例中、我们希望使用相同的机制、但将端口3连接到主机端口。 按照我们的理解、如果将端口5替换为主机端口、则端口3不再发送暂停帧。

此外、我们过去观察到主机端口没有中断、这意味着从主机端口本身以及尝试转发数据的外部端口看不到中断。

谢谢您、

此致、

Wissam

尊敬的 Wissam:

soc 在本例中、我们希望相同的机制能够正常工作、但端口3连接到主机端口。 按照我们的理解、如果将端口5替换为主机端口、端口3将不再发送暂停帧。

是、主机端口是 CPSW 的内部端口、 不会发送暂停帧、并阻止主机端口 FIFO。

有关主机端口的预期不正确、上述摘要更新中提供了说明。

此外、我们过去观察到主机端口没有中断、这意味着从主机端口本身以及尝试转发数据的外部端口看不到中断。

是的、这些 将在主机端口 Rx FIFO 之后在 UDMA 内部丢弃。

此致、

Sudheer