Thread 中讨论的其他器件:TDA4VL、 SysConfig

工具/软件:

尊敬的专家

这是这个主题的延伸讨论、

因为客户尝试使用1GB LPDDR4的定制板启动 CCS 调试、我看到了此错误消息

因此、我认为应该是 DDR 初始化问题、请发布该线程以进行 DDR 设置双重检查。

721S2 Running the DDR configuration... Wait till it completes! Error evaluating "J7_LPDDR4_Config_Late()": Target failed to read 0x80114080 at (*((unsigned int*) (0x80000000U+fsp_clkchng_req_addr))&0x80) [J7_DDR_Config.gel:3337] at DDRSS_LPDDR4_Ack_Freq_Upd_Req(ddrss_num) [J7_DDR_Config.gel:3413] at J7_LPDDR4_Config_Single(0) [J7_DDR_Config.gel:3699] at J7_LPDDR4_Config() [J7_DDR_Config.gel:3734] at J7_LPDDR4_Config_Late() (C:\src\0506\launch.js#130)

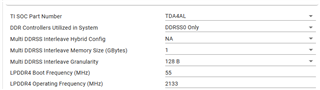

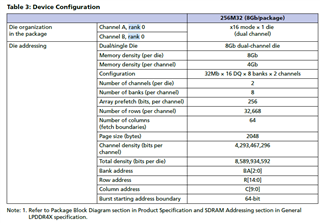

(1) Pls 检查基本设置、正确吗?

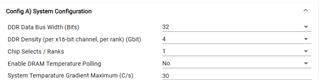

(2) plc check Config A、System Configuration、是否正确?

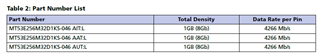

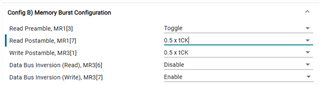

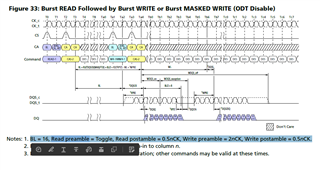

(3)配置 B、存储器突发配置、正确吗?

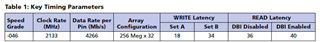

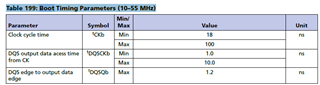

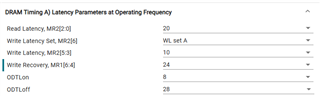

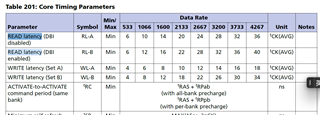

(4) DRAM 时序 a)工作频率下的延迟参数、正确吗?

DDR SYS 配置为连接

e2e.ti.com/.../tda4al_5F00_1g_5F00_ddr.syscfg

谢谢你。

Gibbs