Thread 中讨论的其他器件: TDA4VH

工具/软件:

尊敬的专家:

与 R5 u-boot 中的 CPU 写入相比、我尝试在 ECC 受保护的 DRAM 区域收集 BIST 写入延迟。

- 参考板: J721E/TDA4参考板

- SDK:TI-PROCESSOR-SDK-LINUX-ADAS-j721e-EVM-10_01_00_04

在第一次测试中、 我在 R5 u-boot 中写入"k3_ddrss_preload_ecc_mem_region ()"函数、

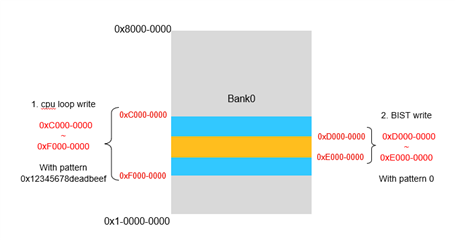

使用 u64 PATTEN 0x1234-5678-DEAD-BALL 在0xC000-0000 ~ 0xD000-0000上写入 CPU 循环

我在 u-boot 提示符下检查 DRAM 内容,它运行良好。

| => MD.l 0xC0000000 0x10 c0000000:死牛肉12345678死牛肉12345678...xV4… XV4。 c0000010:死牛肉12345678死牛肉12345678...xV4… XV4。 c0000020:死牛肉12345678死牛肉12345678...xV4 XV4。 c0000030:死牛肉12345678死牛肉12345678...xV4… XV4。 => MD.l 0xcfffe0 0x10 cfffffe0:死牛肉12345678死牛肉12345678...xV4… XV4。 cffffff0:死牛肉12345678死牛肉12345678...xV4… XV4。 d0000000:008a81c1 c00090f4 1c100002 01809008… d0000010:82884431 cca20202 8010a8 65924309一维.......... C.E. => |

在第二个测试中、 在 CPU 写入0xC000-0000 ~ 0xD000-0000之后 、 R5 u-boot 中带有模式0x1234-5678-dead-beef

然后我调用 u-boot 函数" K3_LPDDR4_BIST_init_mem_region (ddrss、0x50000000、0x10000000、0x11223344) "

以 u32图形0x1122-3344初始写入0xD000-0000 ~ 0xE000-0000

但执行以下操作会导致 u-boot 提示符

| => MD.l 0xC0000000 0x10 c0000000:死牛肉12345678死牛肉12345678...xV4… XV4。 c0000010:死牛肉12345678死牛肉12345678...xV4… XV4。 c0000020:死牛肉12345678死牛肉12345678...xV4 XV4。 c0000030:死牛肉12345678死牛肉12345678...xV4… XV4。 => MD.l 0xc71e0 0x10 c71c71e0:死牛肉12345678死牛肉12345678...xV4… XV4。 c71c71f0:死牛肉12345678死牛肉12345678...xV4… XV4。 c71c7200:11223344 11223344 00000000 D3".d3"…… c71c7210:11223344 11223344 00000000 D3".D3"…… => MD.l 0xd5555560 d55560:11223344 11223344 00000000 D3".d3"…… d5555570: 11223344 11223344 00000000 D3".d3"…… d5555580:c8108008 14042783 091d0400 141289c4… ".... d55590:0b894888 411488ac 410a9198 8201d814 .h A...A.... => |

BIST 写入似乎遇到2个问题:

- 不期望 DRAM 范围 c71c7200 ~ d55580。

- 某些区域不会用零而不是图形初始化。

下面是我在第二次测试中的 u-boot 代码、您能帮助检查出什么问题吗?

| 文件: TI-PROCESSOR-SDK-LINUX-ADAS-j721e-evm-10_01_00_04/board-support/ti-u-boot-2024.04+git/drivers/ram/k3-ddrss/k3-ddrss.c |

| 静态 void k3_ddrss_preload_ecc_mem_region (u64 * addr、u64大小、u64模式) { u64 i = 0; 对于(I = 0;I <(SIZE / 8);I++) Addr[i]=模式; } |

|

静态 void k3_ddrss_lpddr4_ecc_init (struct k3_ddrss_desc *ddrss) // 跳过 DONE = GET_TIMER (0); DONE = get_timer (0); // BIST 需要总线地址? 我是对的吗? (0xD000-0000 - 0x8000-0000)= 0x5000-0000 //跳过 } |

非常感谢您的支持!

此致、

Leon