主题中讨论的其他器件:AM62L、 SysConfig

工具/软件:

您好、

在哪里可以找到模块 ID 和时钟列表? 似乎不能像 Am62x 那样点击

谢谢、

Dazong

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

工具/软件:

您好、

在哪里可以找到模块 ID 和时钟列表? 似乎不能像 Am62x 那样点击

谢谢、

Dazong

您好、Dazong、

上述 API 用于获取所有外设模块的时钟频率。

因此、如果您想知道任何外设的工作频率、只需传递模块 ID 和时钟 ID。

工作频率结果应在 clockrate 变量中可用。

通常、我们需要将这些详细信息添加到 SCI 文档中。 我需要查看这些详细信息。

目前、请使用以下文件获取时钟 ID 和外设 ID。

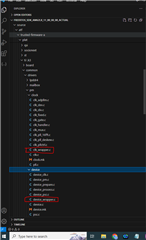

C:\ti\freertos_sdk_am62lx_11_00_00_05\source\drivers\scp\scmi\scm\am62lx soc

此致、

Anil.

Dazong,

以下链接有助于获取有关外设运行频率即频率的详细信息。

此致、

Anil.

尊敬的 Anil:

我们的硬件验证软件的前几行将打印模块频率、以便确保它们以正确的速度运行。

我们读取的25MHz 带有 AM62Lx_DEV_DDR16SS0、时钟值为0和1、似乎错了。 请检查您这边的值吗? 我们使用 SDK 中的 tiboot3.bin。

SoC_moduleGetClockFrequency (AM62LX_DEV_DDR16SS0、0、&clkrate)

SoC_moduleGetClockFrequency (AM62LX_DEV_DDR16SS0、1、&clkrate)

谢谢、

Dazong

您好、Dazong、

请使用下面的链接传递时钟 ID 以获取特定的外设 频率。

尝试使用302而不是0、然后查看您是否能够获得50MHz 时钟。

https://github.com/TexasInstruments/arm-trusted-firmware/blob/ti-master/docs/plat/ti-am62l.rst

此致、

Anil.

您好、Dazong、

为了验证 AM62L SOC 上的 DDR 频率、我确定了两种可能的软件方法。 下面是每种方法的详细说明。

方法1:监控其他外设中的 DDR PLL 输入使用情况

方法:

•DDR PLL 输入时钟由多个外设(例如、计时器、其他高速接口)使用。

•如果任何外设共享该时钟,我们可以监控该外设的时钟配置。

•在 AM62L 中、DDR PLL 输入时钟不与任何其他 IP 共享-它仅专用于 DDR 子系统。

由于没有其他外设可以间接监控 DDR 频率、因此该方法不适用。

方法2:检查输入到 DDR 输出时钟的 PLL 比例因子

方法:

•我们不会监视另一个 IP、而是检查时钟树配置以确定 DDR 频率。

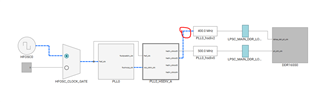

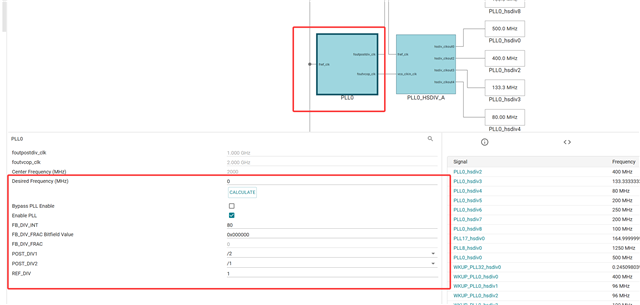

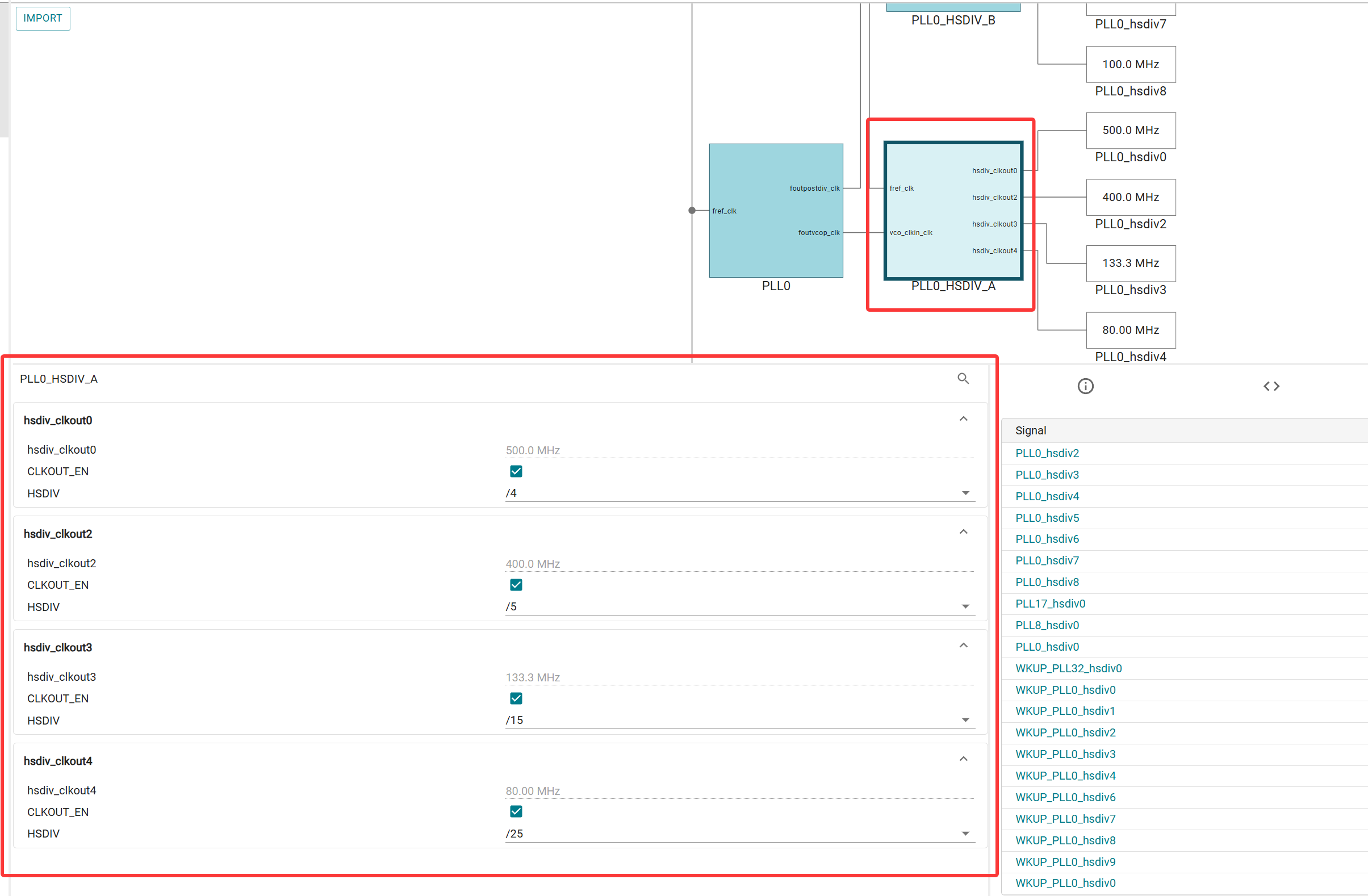

•PLL 的输入时钟为25MHz、它通过 PLLHSDIVA 块生成 DDR 频率。

•要监测的关键参数是 HSDIVCLKOUT2、它负责提供最终的 DDR 时钟。

•通过读取 HSDIVCLKOUT2的比例因子、我们可以确认是否生成了预期的频率。

AM62L 中的实现:

DDR PLL 接收25MHz 输入时钟。

2. PLLHSDIVA 块使用分频器(HSDIVCLKOUT2)缩放此输入。

3。预期比例因子为5、因此 DDR 时钟为25MHz× 5 = 400MHz。

4.通过检查 HSDIVCLKOUT2比例因子是否设置为5、我们可以确认 DDR 在400MHz 下运行。

请确保、您不应在该寄存器中设置任何会影响 DDR 的值。

此致、

Anil.

您好、Dazong、

DDR 时钟初始化和配置在 TF 阶段1中完成(仅限阶段)。

您可以在下面查看这些详细信息。

此致、

Anil.

尊敬的 Anil:

1)如会议所述、让我从 DDR4的输入时钟频率了解 TI 的情况。

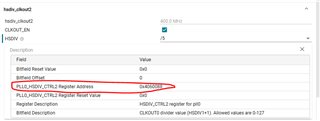

根据您读取值的建议方法、我得到了

FB_DIV_INT = 80

hsdiv = 4

我想它在500MHz 上运行。

2)在会议中,我讨论了 I2C 时钟频率问题。 因为我们正在逐个实施模块。 您希望我测试所有模块并一次性提供所有 Matter、还是希望我逐个模块更新此模块

谢谢、

Dazong

您好、Dazong、

在会议中、我讨论了 I2C 时钟频率问题。 因为我们正在逐个实施模块。 您希望我测试所有模块并一次性提供所有重要内容、还是希望我按模块更新此模块

是的、上面的一个对所有模块进行有意义和完整的测试、并在一条不起作用的注释中分享所有详细信息。

我们可以一次性修复它们。

[引用 userid="628999" url="~/support/processors-group/processors/f/processors-forum/1488462/tmds62levm-how-to-use-soc_modulegetclockfrequency/5757517 #5757517"]hsdiv = 4

我想它在500MHz 上运行。

[/报价]您能否确认您正在读取的寄存器地址是哪一个?

此致、

Anil.

1)如会议所述、让我从 DDR4的输入时钟频率了解 TI 的情况。

根据您读取值的建议方法、我得到了

FB_DIV_INT = 80

hsdiv = 4

我想它在500MHz 上运行。

[/报价]您好、Dazong、

根据时钟配置和测试结果:

•活动 HSDIV 值设置为4。

•在时钟树计算中、使用的公式为:

有效分频器= HSDIV + 1、

实际分压器变为5。

•给定基础频率时、生成的 DDR 输入时钟为:

基本频率/5 = 400 MHz。

在 DDRSS (DDR 子系统)中:

•DDR PHY 和 EMIF 模块在内部将400 MHz 时钟乘以2、从而产生800 MHz DDR 时钟。

•由于 DDR (双倍数据速率)同时在时钟的上升沿和下降沿传输数据、因此有效数据速率变为:

800 MHz× 2 = 1600MT/s (每秒兆次传输)。

此致、

Anil.

您好、Dazong、

是的、TRM 中目前并未提及此信息。

但是、我参考了 AM62L 时钟 IP 规范文档、据此、DDRSS 输出时钟固定在800 MHz。

遗憾的是、我无法与您共享此内部文档、但为了供您参考、您可以将 DDRSS 输出视为始终在800 MHz 中运行。

我还将咨询硬件专家、了解我们如何在未来的修订版本中将此详细信息整合到 TRM 中。

此致、

Anil.

尊敬的 Anil:

我现在正在分析 TF-A。 您能验证我是否查看了正确的时钟设置文件吗?

PLL:ti-processor-sdk-linux-am62lxx-evm-11.00.00.00.03\board-support\ 受信任的固件 -a-2.11+git\plat\ti\k3\am62l\scmi\drivers\am62lx\ soc clocks

措辞:ti-processor-sdk-linux-am62lxx-evm-11.00.00.00.03\board-support\ TI-u-boot -2024.10+git\dts\上游\Arm64\ti\ src k3-am62l-main.dtsi

我应该查看的任何其他文件? 我尝试实现的是确保时钟设置、然后将值放入

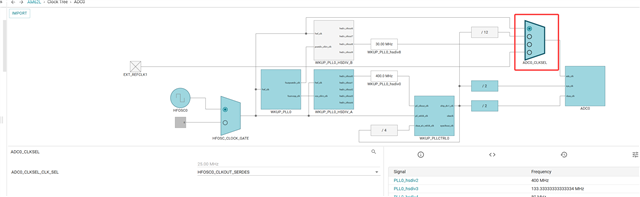

使用网站的可视输出,比较来自 SOC_ModuelGetClockFrequency ()的结果

例如这些字段

从 USB DFU 引导时、我不确定是否从 uboot 设置了外设

谢谢、

Dazong

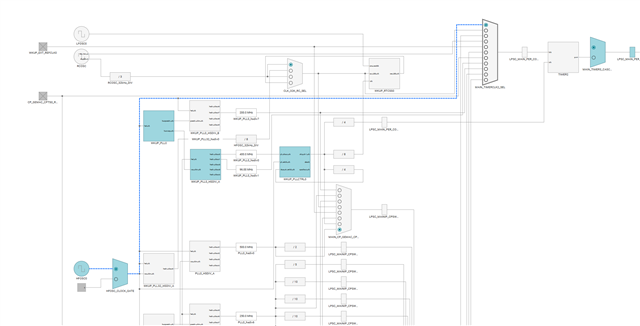

您好、Dazong、

请查看 SCMI 呼叫流程。

应用程序请求为特定 IP 设置时钟或打开或关闭 PSC。

该请求会在控件跳转到 ATF 时写入共享存储器。

ATF 将决定是否执行特定操作是时钟设置还是 GET 或 PSC ON 或 OFF。

因此、在 ATF 文件夹的第一级、您可以检查这些包装器文件。

ATF 请求这些调用来执行时钟设置或 PSC 开/关操作。

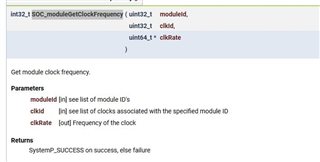

int32_t SOC_moduleGetClockFrequency(uint32_t moduleId, uint32_t clkId, uint64_t *clkRate);

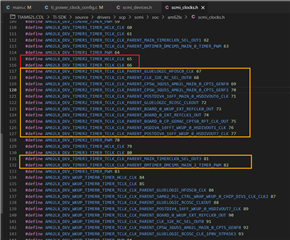

要获取时钟 ID、我们需要传递模块 ID 和时钟 ID、这些 ID 可在以下 below.h 文件中找到。

因此、您需要使用这些文件来获取特定的 IP 频率。

所有 PLL 设置均由 ROM 引导加载程序完成、同样、用户无需触摸它们。

我不确定您是否要更新或重新配置不同的 PLL 设置?

为什么要更改 PLL 设置?

请告诉我、以上答复已解决了您的疑问。

此致、

Anil.

尊敬的 Anil:

我们有两个问题:

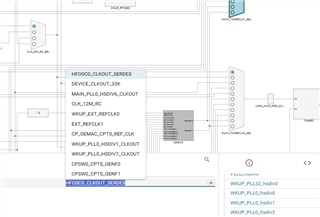

1)我们尝试使用 ti_power_clock_config.c 中的 gSocModuleClockFrequency[]设置计时器模块(计时器2和3)的时钟频率 当我们使用下面的 SysConfig 中所示的 HFOSC0_CLKOUT_SERDE 等选择时钟时、我们无法使 TFA 成功引导:

SOC_ModuleClockFrequency gSocModulesClockFrequency[] = {

{ AM62LX_DEV_TIMER2, AM62LX_DEV_TIMER2_TIMER_TCLK_CLK_PARENT_GLUELOGIC_HFOSC0_CLK, 25000000 },

//{ AM62LX_DEV_TIMER3, AM62LX_DEV_TIMER2_TIMER_TCLK_CLK_PARENT_GLUELOGIC_HFOSC0_CLK, 25000000 },

{ SOC_MODULES_END, SOC_MODULES_END, SOC_MODULES_END },

};

a)我们如何才能使其正常工作?

b)标有红色的两个时钟来自哪里?

c)计时器3没有像计时器2那样的11个时钟多路复用器选项、它们是否在内部连接?

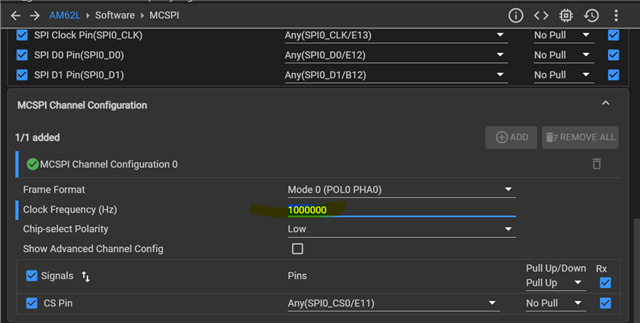

2)我们还尝试使用下面的片段为 MCSP1设置不同的频率。

SOC_ModuleClockFrequency gSocModulesClockFrequency[] = {

{ AM62LX_DEV_MCSPI1, AM62LX_DEV_MCSPI1_CLKSPIREF_CLK, 2400000000 },

{ SOC_MODULES_END, SOC_MODULES_END, SOC_MODULES_END },

};

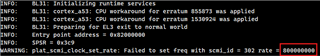

但是、我们注意到、当使用某些时钟频率(例如2.4GHz、1000MHz、800MHz、700MHz、500MHz 等)时、TFA 引导无法完成

而1.2GHz、600MHz、400MHz、300MHz、200MHz 等其他频率似乎可以正常工作。

这是什么原因?

此致、

Simeon

a)我们如何才能使其正常工作?

[/报价]您好 Simeon、

SoC 中的所有计时器都有一个针对其输入时钟源的多路复用器选择机制。

计时器时钟(TCLK)源

•TCLK 指计时器输入时钟、它源自时钟多路复用器的输出。

•例如、要选择 HFOSC 作为 TIMER2的输入时钟、以下参数是正确的:

AM62LX_DEV_TIMER2_TIMER_TCLK_PARENER_GLUELOGIC_HFO SC0_CLK

/* ----------- TimerP ----------- */

#define CONFIG_TIMER0_CLOCK_SRC_MUX_ADDR (0x9117000u)

#define CONFIG_TIMER0_CLOCK_SRC_HFOSC0_CLKOUT (0x0u)

/* set timer clock source */

SOC_controlModuleUnlockMMR(SOC_DOMAIN_ID_MAIN, 2);

*(volatile uint32_t*)AddrTranslateP_getLocalAddr(CONFIG_TIMER0_CLOCK_SRC_MUX_ADDR) = CONFIG_TIMER0_CLOCK_SRC_HFOSC0_CLKOUT;

SOC_controlModuleLockMMR(SOC_DOMAIN_ID_MAIN, 2);

尊敬的 Anil:

我们正在研究的仍然是外设的输入时钟。

我们要使用的文件是 ti_power_clock_config.c

uint32_t gSocModules[]; SOC_ModuleClockFrequency gSocModulesClockFrequency[]; void Module_clockEnable(void);

{ AM62LX_DEV_TIMER2, AM62LX_DEV_TIMER2_TIMER_TCLK_CLK_PARENT_GLUELOGIC_HFOSC0_CLK, 25000000 },2.当使用 MCSPI 输入时钟频率时,我们观察到它可以设置为50MHz 以外的其他值,如100MHz ,并且 SOC_ModuleGetClockFrequency()也将返回100MHz。 我猜测 hsdiv_clkout6正在做一些事情、因为可以将除法设置为/1到/128之间的值。 我们要尝试一些不超过2.4GHz 的值

{ AM62LX_DEV_MCSPI1, AM62LX_DEV_MCSPI1_CLKSPIREF_CLK, 2400000000 },

正如 Simeon 提到的、"1.2GHz、600MHz、400MHz、300MHz 200MHz 似乎工作"。 "使用的时钟频率如2.4GHz、1000MHz、800MHz、700MHz、500MHz 等将失败"

{ AM62LX_DEV_MCSPI1, AM62LX_DEV_MCSPI1_CLKSPIREF_CLK, 600000000 },

SOC_moduleGetClockFrequency(AM62LX_DEV_MCSPI1, AM62LX_DEV_MCSPI1_CLKSPIREF_CLK, &clkRate);

info("MCSPI1 CLK RATE: %d\n", clkRate);

Print: MCSPI1 CLK RATE: 600000000

我想这最终是两个问题。

1.如果我们要更改 HSDIV 的值、是否建议使用 CSL_REG32_WR ()直接更改寄存器本身?

2.如果我们要更改多路复用器输入(如 timer2的情况)、为什么有效的父时钟名称 AM62LX_DEV_TIMER2_TIMER_CLK_PARENER_GLUELOGIC_HFOSC0_CLK 不工作、整个应用程序就卡滞了

谢谢、

Dazong

尊敬的 Anil:

尝试直接配置计时器的多路复用器寄存器后、我看不到时钟频率变化、仍会获得100MHz。 使用 CONFIG_TIMER0_CLOCK_SRC_MUX_ADDR)= CONFIG_TIMER0_CLOCK_SRC_HFOSC0_CLKOUT 时、我认为它应该是25MHz、因为它直接来自 HFO?

SOC_controlModuleUnlockMMR(SOC_DOMAIN_ID_MAIN, 2);

*(volatile uint32_t*)AddrTranslateP_getLocalAddr(CONFIG_TIMER0_CLOCK_SRC_MUX_ADDR) = CONFIG_TIMER0_CLOCK_SRC_HFOSC0_CLKOUT;

SOC_controlModuleLockMMR(SOC_DOMAIN_ID_MAIN, 2);

计时器 CLK 速率:100000000

谢谢您、

Dazong

尝试直接配置计时器的多路复用器寄存器后、我看不到时钟频率变化、仍在获取100MHz。 使用 CONFIG_TIMER0_CLOCK_SRC_MUX_ADDR)= CONFIG_TIMER0_CLOCK_SRC_HFOSC0_CLKOUT 时、我认为它应该是25MHz、因为它直接来自 HFO?

您好、Dazong、

是、上述多路复用器设置为 HFOSC 时钟。 计时器仅在25MHz 下运行、而不在100MHz 下运行。

您能否确认您是如何确认计时器在100MHz 运行的?

你从 ATF 读了吗?

此致、

Anil.

您好、Dazong、

使用当前多路复用器设置、计时器在25 MHz 下运行。 我建议将计时器配置为生成10ms 的中断、然后验证实际的中断间隔以确认行为。

SOC_moduleGetClockFrequency

SCMI 时钟频率调用似乎返回了不正确的值。 这是因为计时器频率未通过 SCMI 接口的多路复用器选择进行设置。 因此、ATF 不知道在应用程序级别配置的预分频器设置、因此采用默认值进行响应。

对于某些外设(如 I2C、SPI 等)、ATF 提供功能时钟(FCLK)速率、并且任何进一步的时钟分频都 是在 IP 级别使用预分频器配置发生的、那么您可能会收到 FCLK、而不是外设工作的实际频率。

我的建议:

始终从 ATF 检索 IP 的基频(FCLK)、然后读取 IP 的预分频器设置。 使用这两个值将可获得外设的准确有效时钟速率。

此致、

Anil.

您好、Dazong、

在进行任何更改之前、请确认 您计划修改哪个 HSDIV。

这一点很重要、因为修改 HSDIV 会影响多个 IP、不正确的变化会导致系统性能下降。

重要注意事项:

•HSDIV 更改会影响使用该输出的所有时钟使用者。

•如果 SoC 的 PLL 通过同一 HSDIV 馈送多个外设、更改其分频器可能会意外减慢多个模块的速度。

关于 ATF 和时钟控制:

•ATF 不会公开简单的 API。

•它将 SCMI (系统控制和管理接口)用于所有器件控制操作(例如时钟、复位和电源域)。

SCMI 时钟和 PSC 控制流程:

1.应用程序将消息写入 SCMI 共享内存。

2.应用程序发出 SMC (Secure Monitor Call)调用 ATF。 在这里,应用程序停止并跳转到 ATF 代码。

3.在 ATF 内部,该消息被解析并发送给 时钟设置/获取和 电源域(PSC)启用/禁用

4. ATF 处理请求,并通过相同的共享内存发回响应。

5、应用程序在 SMC 返回后读取结果。

建议检查的文件:

要了解 SET_CLOCK、GET_CLOCK 和 PSC 启用的完整流程、请执行以下操作:

•从代码中的 SCMI 协议层开始。

•跟踪通过特定于平台的服务处理程序的流量。

•然后、调用进入内部时钟/PSC 驱动程序层(不是单个 API、它是一个链接调用流程)。

以下代码位于 ATF 侧、因此当 SCMI 调用基于 SET、GET 或 PSC 启用的请求时、ATF 会调用特定的 API。

此致、

Anil.