主题中讨论的其他器件:SysConfig、 TDA4VL

工具/软件:

尊敬的 TI

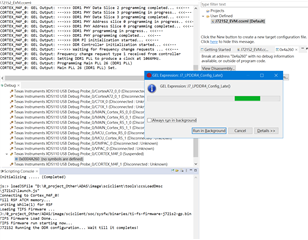

我们想使用 CCS 运行.out 文件进行检查

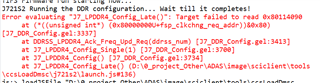

但是、我们停止在"运行 DDR 配置的 J721S2。 等它完成!"

并具有以下错误日志

你有什么评论吗?

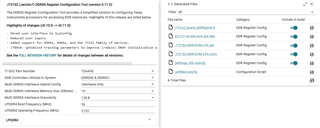

我们使用 pdk_j721s2_10_01_00_25和8GB DDR 存储器(mt53e2g32d4de-046)

TI 的默认设计看起来像16GB、

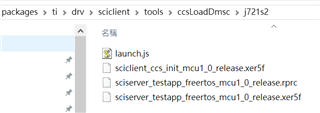

我是否需要对 sciclient_ccs_init_mcu1_0_release.xer5f 和 sciserver_testapp_freertos_mcu1_0_release.xer5f 进行一些修改和重新编译 ?

非常感谢