工具/软件:

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

工具/软件:

问题描述:相同的型号、推断相同的图像。 使用 TIDL 仿真工具获得的结果是正常现象。 但是、在评估板上运行推理时、结果异常。 比较两者的二进制结果可以发现、大多数部件都是相同的、匹配的部件对应于分段结果、这种验证是正确的。 两者之间二进制结果不同的部分对应于错误结果。

原始型号:

e2e.ti.com/.../segod_5F00_res18_5F00_410.zip

转换后的模型:

e2e.ti.com/.../tidl_5F00_io_5F00_seg_5F00_1.zip

e2e.ti.com/.../tidl_5F00_net_5F00_seg.zip

仿真推理结果:

e2e.ti.com/.../seg_5F00_out.zip

评估板推理结果:

e2e.ti.com/.../em_5F00_seg_5F00_output_5F00_nopad.zip

二进制比较结果:

示例图像:

每个层输出的浮点数:

e2e.ti.com/.../seg_5F00_double_5F00_result.zip

其他信息:

在 PC 上获得的推理结果、我们认为是正确的

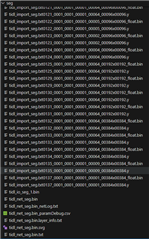

导入配置:

e2e.ti.com/.../tidl_5F00_import_5F00_seg.txt

导入日志:

e2e.ti.com/.../seg_5F00_0527.log

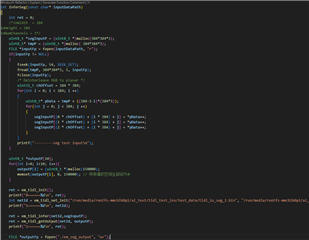

我通过在 PC 上进行模型转换期间添加参数 writeTraceLevel = 3来获得每层的结果。 我将二进制文件中的每4个字节转换成一个浮点、然后将它们存储在一个 txt 文件中。 如下图所示:

推断配置:

e2e.ti.com/.../config_5F00_list_5F00_seg.txte2e.ti.com/.../tidl_5F00_infer_5F00_seg.zipe2e.ti.com/.../test_5F00_seg.txt

你(们)好

您也可以在 EVM 上试用吗?

上的模型转换期间添加参数 writeTraceLevel = 3来获得每层的结果I 通过在 PC

您可能会看到一个名为"trace"的文件夹、您可以在其中执行可执行文件、图层结果将保存到该文件夹中。 如果没有"trace"文件夹、也可以检查/tmp 文件夹

这些步骤的目标是了解哪个层会开始产生这种不匹配情况、并有助于进一步调试

此致、

Adam

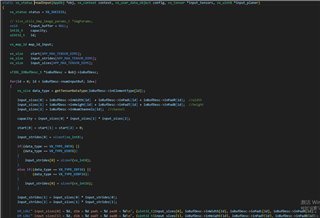

在 EVM 上、我们使用封装的 vision_apps 执行推理。

如何设置 writeTraceLevel = 3以输出每个图层的结果?

关键代码片段:

源代码:

e2e.ti.com/.../2262.main.ce2e.ti.com/.../app_5F00_tidl_5F00_em.zip