主题:AM6421 中讨论的其他器件

工具/软件:

您好、

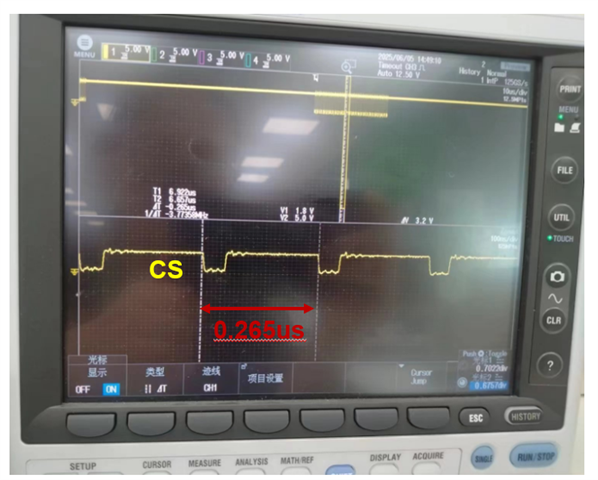

当 使用 AM6421 GPMC 与 FPGA 通信时、 两次读取之间的延时时间似乎非常长。 在测试中、延迟约为 0.26us、如下图所示。 黄线是 CS 信号。

我的问题是:

1 为什么即使我们将周期延迟设置为无延迟、两次读取之间的延迟也是如此长?

2 如何减少两次读取之间的延时时间?

3 两次写入之间显示了相同的延迟。 如何减少两次写入之间的延时时间?

我们不想使用 GPMC 突发模式、因为在 FPGA 编码方面会有很多工作。

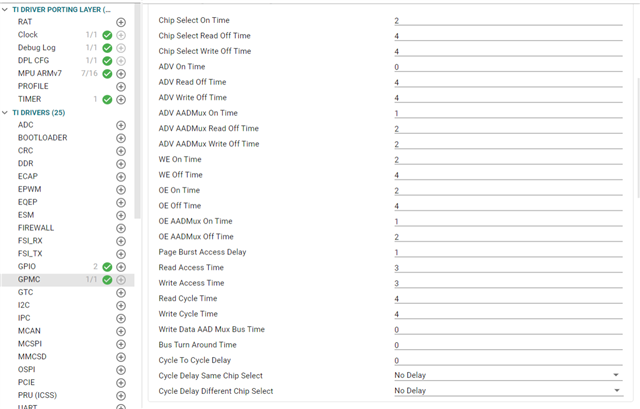

GPMC 配置如下所示。

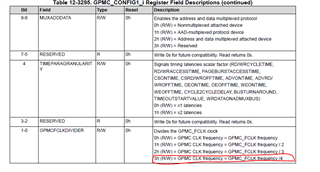

配置了同步单次写入和读取模式。 启用 WAIT 引脚。 时序参数如下所示

从 FPGA 读取的代码如下:

volatile uint16_t *pSrc =(volatile uint16_t *)(offset + BASEADDRESS_CS0);

Volatile uint16_t *pDst =(volatile uint16_t *) test_gpmcRxBuf;

for (I = 0;I<16;I++)

{

*pDst =*pSrc;

pSrc++;

pDst++;

}

谢谢!