工具/软件:

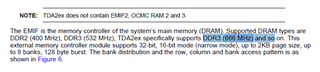

TDA2PHVx 支持的 DDR3 时钟是什么? 我看到在不同的 TI 规格中有不同的值

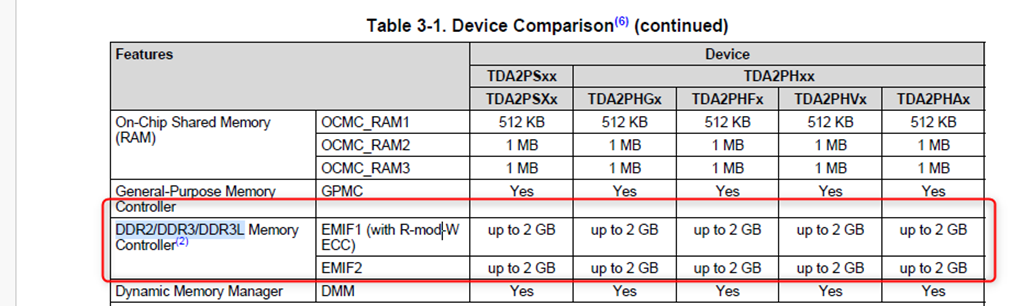

在下图中、TDA2Ex 仅支持 666MHz、而在第二个图中、TDA2Px 支持 666MHz

TDA2PHVx 支持 DDR3 的理论带宽是多少? 实际带宽是多少? 我知道它取决于 clk、因此这需要与第一个问题相关

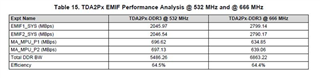

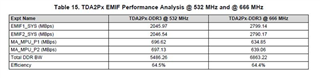

下面的两张图片显示了这一点

- EMIF BW @532MHz = 2045.97 +2046.54 (假设连接了两个 EMIF)=~4091

- EMIF BW @666MHz = 2799.14 + 2790.17 (假设连接了两个 EMIF)=~5589 ->这是正确的吗? 即使是第二个规范状态最大值 2 GB?

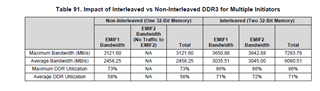

-在第三张图片中,交错式 DDR 的最大 BW 为 7293.76MByte/s 适用于哪种 SoC? 这是否适用于 TDA2PHVx