请注意,本文内容源自机器翻译,可能存在语法或其它翻译错误,仅供参考。如需获取准确内容,请参阅链接中的英语原文或自行翻译。

器件型号:AM625-Q1 工具/软件:

您好、

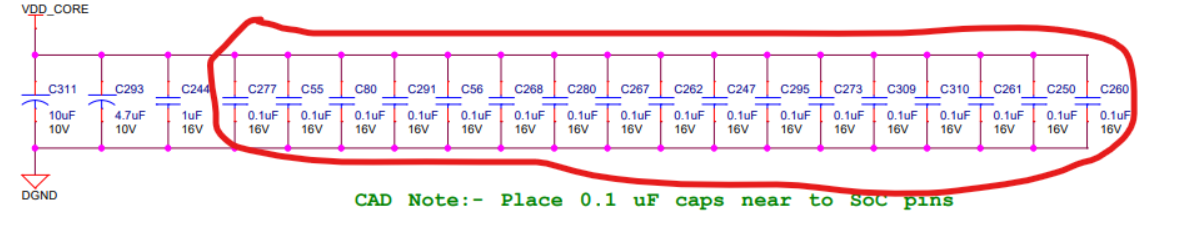

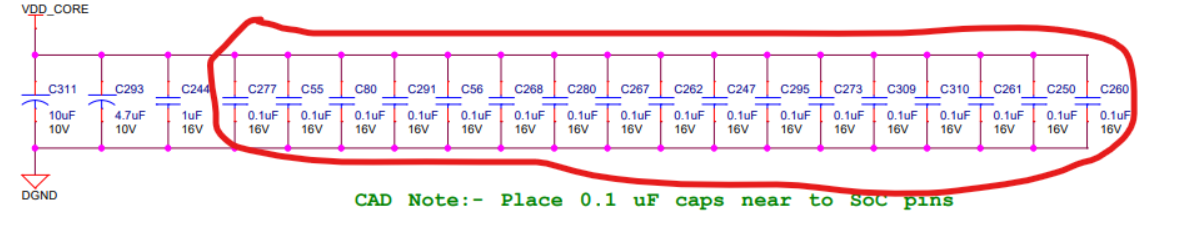

根据评估板原理图、为每个引脚添加了一个电容器 (100nF)、重复引脚?

例如:用于 VDD_CORE 16 个引脚的 16 个去耦电容器

是否必须使用这些 数量的电容器? 我们可以减少电容吗?

此致

Soumya.

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

工具/软件:

您好、

根据评估板原理图、为每个引脚添加了一个电容器 (100nF)、重复引脚?

例如:用于 VDD_CORE 16 个引脚的 16 个去耦电容器

你好 Soumya

感谢您的查询。

建议遵循 PDN 文档。

https://www.ti.com/lit/an/sprac76g/sprac76g.pdf

表 7-6. AM62xx PDN 目标和去耦示例

或者、建议执行仿真以优化电容器。

此致、

Sreenivasa.