主题中讨论的其他器件: AB15

工具/软件:

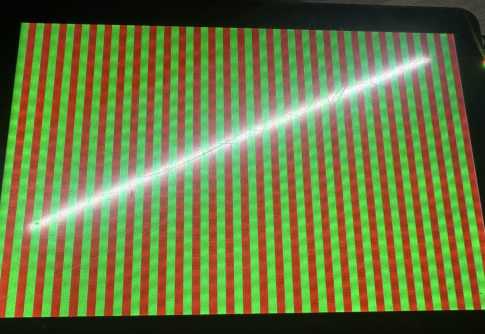

MIPI-DSI 已连接到 mipi 屏幕、但当前未显示该屏幕。

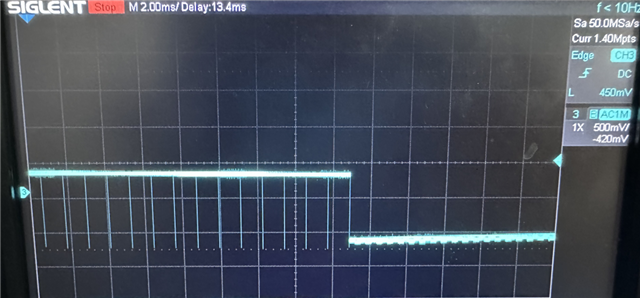

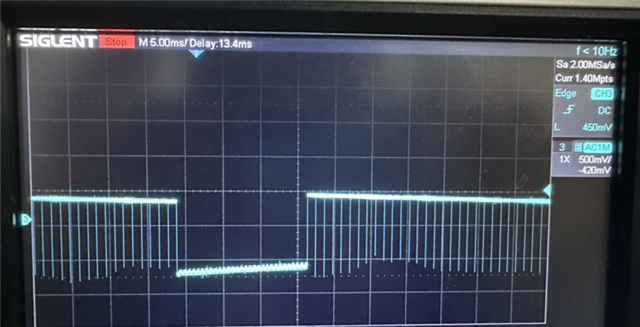

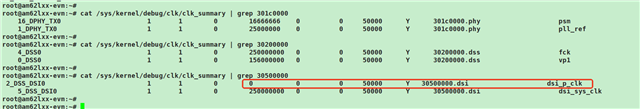

请注意 dsi_p_clk 不速率、为什么会这样?如何对问题进行故障排除? 请提供指南。

使用命令“modetest -M tidss““cat /sys/kernel/debug/dri/30200000.dss/state “"kmsprint"查看“查看以下“以下内容:

root@am62lxx-evm:~# kmsprint

[ 984.281069] mipi rad panel get mode

Connector 0 (41) DSI-1 (connected)

Encoder 0 (40) NONE

Crtc 0 (39) 1200x1920@58.53 156.000 1200/80/24/60/- 1920/20/4/10/- 59 (58.53) 0xa 0x48

Plane 0 (32) fb-id: 43 (crtcs: 0) 0,0 1200x1920 -> 0,0 1200x1920 (AR12 AB12 RA12 RG16 BG16 AR15 AB15 AR24 AB24 RA24 BA24 RG24 BG24 AR30 AB30 XR12 XB12 RX12 XR15 XB15 XR24 XB24 RX24 BX24 XR30 XB30 YUYV UYVY NV12)

FB 43 1200x1920

root@am62lxx-evm:~#

root@am62lxx-evm:~#

root@am62lxx-evm:~#

root@am62lxx-evm:~# modetest -M tidss

[ 1015.324690] mipi rad panel get mode

Encoders:

id crtc type possible crtcs possible clones

40 39 none 0x00000001 0x00000001

Connectors:

id encoder status name size (mm) modes encoders

41 40 connected DSI-1 135x216 1 40

modes:

index name refresh (Hz) hdisp hss hse htot vdisp vss vse vtot

#0 1200x1920 58.53 1200 1280 1304 1364 1920 1940 1944 1954 156000 flags: nhsync, nvsync; type: preferred, driver

props:

1 EDID:

flags: immutable blob

blobs:

value:

2 DPMS:

flags: enum

enums: On=0 Standby=1 Suspend=2 Off=3

value: 0

5 link-status:

flags: enum

enums: Good=0 Bad=1

value: 0

6 non-desktop:

flags: immutable range

values: 0 1

value: 0

4 TILE:

flags: immutable blob

blobs:

value:

42 panel orientation:

flags: immutable enum

enums: Normal=0 Upside Down=1 Left Side Up=2 Right Side Up=3

value: 0

CRTCs:

id fb pos size

39 43 (0,0) (1200x1920)

#0 1200x1920 58.53 1200 1280 1304 1364 1920 1940 1944 1954 156000 flags: nhsync, nvsync; type: preferred, driver

props:

24 VRR_ENABLED:

flags: range

values: 0 1

value: 0

27 CTM:

flags: blob

blobs:

value:

28 GAMMA_LUT:

flags: blob

blobs:

value:

29 GAMMA_LUT_SIZE:

flags: immutable range

values: 0 4294967295

value: 256

Planes:

id crtc fb CRTC x,y x,y gamma size possible crtcs

32 39 43 0,0 0,0 0 0x00000001

formats: AR12 AB12 RA12 RG16 BG16 AR15 AB15 AR24 AB24 RA24 BA24 RG24 BG24 AR30 AB30 XR12 XB12 RX12 XR15 XB15 XR24 XB24 RX24 BX24 XR30 XB30 YUYV UYVY NV12

props:

8 type:

flags: immutable enum

enums: Overlay=0 Primary=1 Cursor=2

value: 1

30 IN_FORMATS:

flags: immutable blob

blobs:

value:

01000000000000001d00000018000000

01000000900000004152313241423132

52413132524731364247313641523135

41423135415232344142323452413234

42413234524732344247323441523330

41423330585231325842313252583132

58523135584231355852323458423234

52583234425832345852333058423330

59555956555956594e56313200000000

ffffff1f000000000000000000000000

0000000000000000

in_formats blob decoded:

AR12: LINEAR(0x0)

AB12: LINEAR(0x0)

RA12: LINEAR(0x0)

RG16: LINEAR(0x0)

BG16: LINEAR(0x0)

AR15: LINEAR(0x0)

AB15: LINEAR(0x0)

AR24: LINEAR(0x0)

AB24: LINEAR(0x0)

RA24: LINEAR(0x0)

BA24: LINEAR(0x0)

RG24: LINEAR(0x0)

BG24: LINEAR(0x0)

AR30: LINEAR(0x0)

AB30: LINEAR(0x0)

XR12: LINEAR(0x0)

XB12: LINEAR(0x0)

RX12: LINEAR(0x0)

XR15: LINEAR(0x0)

XB15: LINEAR(0x0)

XR24: LINEAR(0x0)

XB24: LINEAR(0x0)

RX24: LINEAR(0x0)

BX24: LINEAR(0x0)

XR30: LINEAR(0x0)

XB30: LINEAR(0x0)

YUYV: LINEAR(0x0)

UYVY: LINEAR(0x0)

NV12: LINEAR(0x0)

34 zpos:

flags: range

values: 0 0

value: 0

35 COLOR_ENCODING:

flags: enum

enums: ITU-R BT.601 YCbCr=0 ITU-R BT.709 YCbCr=1

value: 0

36 COLOR_RANGE:

flags: enum

enums: YCbCr limited range=0 YCbCr full range=1

value: 1

37 alpha:

flags: range

values: 0 65535

value: 65535

38 pixel blend mode:

flags: enum

enums: Pre-multiplied=0 Coverage=1

value: 0

Frame buffers:

id size pitch

root@am62lxx-evm:~#

root@am62lxx-evm:~#

root@am62lxx-evm:~#

root@am62lxx-evm:~# cat /sys/kernel/debug/dri/30200000.dss/state

plane[32]: plane-0

crtc=crtc-0

fb=43

allocated by = [fbcon]

refcount=2

format=XR24 little-endian (0x34325258)

modifier=0x0

size=1200x1920

layers:

size[0]=1200x1920

pitch[0]=4800

offset[0]=0

obj[0]:

name=0

refcount=2

start=00100000

size=9216000

imported=no

dma_addr=0x00000000bcf00000

vaddr=000000009718aacd

crtc-pos=1200x1920+0+0

src-pos=1200.000000x1920.000000+0.000000+0.000000

rotation=1

normalized-zpos=0

color-encoding=ITU-R BT.601 YCbCr

color-range=YCbCr full range

color_mgmt_changed=0

crtc[39]: crtc-0

enable=1

active=1

self_refresh_active=0

planes_changed=1

mode_changed=0

active_changed=0

connectors_changed=0

color_mgmt_changed=0

plane_mask=1

connector_mask=1

encoder_mask=1

mode: "1200x1920": 59 156000 1200 1280 1304 1364 1920 1940 1944 1954 0x48 0xa

connector[41]: DSI-1

crtc=crtc-0

self_refresh_aware=0

max_requested_bpc=0

colorspace=Default

root@am62lxx-evm:~#

root@am62lxx-evm:~#