主题中讨论的其他器件:DP83869、 TMDS64EVM

工具/软件:

您好、

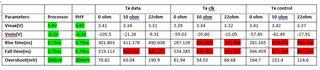

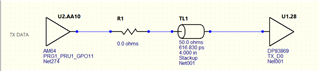

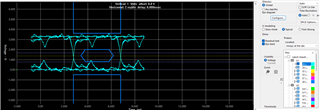

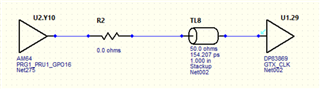

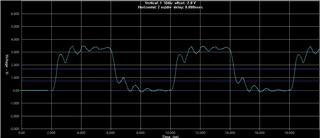

我负责使用 125MHz 处的 RGMII 接口对 AM6442BSFGHAALV 处理器和 DP83869HMRGZT PHY 进行信号完整性分析 。 对于在驱动器侧(处理器)使用 1 英寸布线和 0Ω 串联电阻的 TX 信号 (TX DATA、TX CLK、TX CTRL)、我观察到了振铃。 当我增大连接到 22Ω 的电阻器时、下降时间超出了 0.75ns 的目标范围、达到了约 1ns。 上升时间也接近可接受范围的边沿。 进一步增加串联电阻会降低信号质量。 我将分享我获得的结果快照以及我们的目标参数范围。 在这种情况下、您能否建议一种更好的终端调优方法?