主题中讨论的其他器件:OMAPL138、

工具/软件:

您好 TI、

我们的核心产品一直在使用 L138 E 电机类型 E ( E =基本安全启动)器件多年来成功使用 ISSI 的 IS43LR16320C (64 MB)、Micron 的 MT46H32M16 (64 MB) 和 MT46H128M16 (256 MB)。 Micron 器件最近已收到制造商的报废通知。

因此、一个自然的 256 MB 替换候选项似乎是 ISSI 的 IS43LR16128B (256 MB)、但是、在我们当前的设计中、我们在使此部件正常运行方面遇到了问题。 当使用 GEL 文件(首先解锁 JTAG 路径)通过 JTAG 下载代码时、ISSI 256MB 部件会工作。 以这种方式加载我们通常的 mDDR 生产测试通过了所有测试。 这些 mDDR 测试将耗尽内部内存。 这建议至少在使用 GEL 文件时正确设置 mDDR 寄存器和时序。

但是、在安全启动状态下尝试使用 ROM 引导加载程序进行引导时、256Mb ISSI 器件当前不起作用。 从不接收带有 256 MB ISSI 部件的设备发出的“完成“字符串(在“跳转并关闭“后挂起)。 ISSI 器件重新检查了所有时序、所有时序看起来都正常、这可以通过使用解锁的 JTAG 以及上述类似的 mDDR 时序进行的成功测试来证明。 我们尝试了通过 UART 进行安全启动(以还配置 mDDR)。 我们还通过打开的 JTAG 将正确绑定的加密闪存映像编程到闪存中、但(安全)闪存启动随后似乎也无法成功配置 mDDR、并且启动过程会尽早停止。 通过 UART(“BOOTME")“)进行安全启动、闪存使用列出的其他器件工作。

这似乎表明 ROM 引导加载程序 (RBL) 在设置 256MB ISSI mDDR 时存在问题。 所有安全启动过程都涉及 RBL。 RBL 配置器通过结构馈送数据、该结构没有 GEL 文件提供的灵活性。 另外、RBL 的确切执行对我们来说是不透明的、因此我们无法检查此情况。

第一次检查时、sprz301m/sprz303h 2.1.5 中的勘误说明似乎描述了我们看到的确切症状(“在所有器件版本上、某些采用状态寄存器读取 (SRR) 支持设计的 mDDR 存储器可能与 OMAPL138 器件不兼容。 这些 mDDR 存储器误解了 DDR2/mDDR 控制器在器件上电复位或冷复位(通过将 RESET 引脚置为有效)之后发送的某些初始化序列命令。 这导致 mDDR 存储器无响应、因为它卡在 SRR 状态而不是返回到空闲状态。“ 更多详细信息:

e2e.ti.com/.../omapl138-mddr-clarifications-about-ddr2-mddr-controller-mddr-usage-note-in-errata

尽管 sprz301m / sprz303h 2.1.5 确实建议了补救措施(“为了确保这些类型的 mDDR 存储器的正确初始化、DDR2/mDDR 控制器必须在上电复位或冷复位后将两个连续 的 mDDR 初始化序列发送到 mDDR 存储器。“)、但是、我们在使用 256 MB ISSI 部件尝试此操作时没有成功。

E2E 问题:

e2e.ti.com/.../omap-l138-doesn-t-securely-boot-from-uart-while-running-from-mddr

似乎与我们也看到的问题有关。

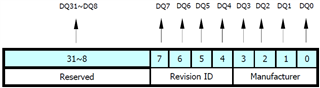

总之、仔细观察上面列出的 mDDR 器件、我们注意到两个 Micron 器件 (64MB 和 256MB) 和小 ISSI 器件 (64MB) 的状态寄存器定义都非常相似、因为位[15:8]有助于描述器件的密度、类型、数据总线宽度和刷新率、例如:

但是、256 MB ISSI 部件(以及同样的 128 MB 产品)在这方面有所不同:

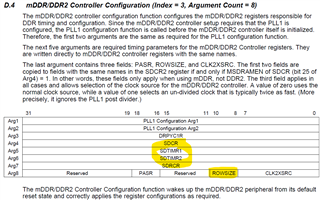

因此、我们目前的理论是、RBL 会出于某种原因解释位[15:8]、并且似乎需要在该处填充有效字段、如上面讨论的其他 mDDR 器件所示。 这可能是必要的原因尚不清楚、因为所有必要的设置值都已在 SDCR 中给出、并且在绑定过程中传递给 RBL 的其他参数也已给出(参见 sprab41d 章节 D.4,也如下所示)。 可能此设置也已加密、因此最初无法在引导期间配置 mDDR 控制器。

请允许我们提出一些问题:

1. TI 能否确认当与未定义的 mDDR 状态寄存器[15:8]位一起显示时、RBL 的预期行为是什么? RBL 是否会以任何方式解释 mDDR 状态寄存器位[15:8]?

2.如果是、RBL 检查 mDDR 状态寄存器是否有必要? RBL 代码是否可用于检查?

3.我们使用命令行工具生成引导脚本。 AISgen GUI(我们尚未成功使用)是否针对此处所述的情况实施了有效的权变措施?

4.是否有人使用 ISSI IS43LR16128B 成功引导这些基本安全启动处理器?

5. TI 是否知道在可预见的生产中还有其他任何 256MB mDDR/LPDDR 器件、我们可以通过其他方式将这些器件保留在生产中? 对 DDR2 进行重新设计似乎没有很好的预后、因为这些部件似乎也在淘汰割草机的道路上。

6.或者 TI 能否建议一种可行的解决方法来继续安全启动完整的映像? 否则、两个阶段的进程可能是可能的、但在生命周期的这一阶段肯定不是一个伟大的主张。

7. TI 是否可能正在考虑使用最新的存储器接口来提供新的后续器件? 鉴于上述情况、这似乎变得越来越紧迫。

希望提供任何建议。