Thread 中讨论的其他器件:TMDS64EVM

工具/软件:

您好、

我正在运行 TMDS64EVM 电路板。 我处于 SBL 阶段、没有操作系统。

我正在初始化 DDR。

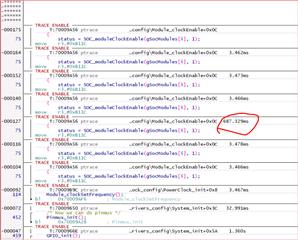

我发现在整个引导过程中、“DDR 使能时钟“需要 700ms。

问题。 这个计时是否合理、是否有绕过的方法?

以及启用 DDR 时钟需要这么长的时间。 我是指整个引导过程、可能小于 1 秒? 使 DDR 时钟占用 60%的时间。

谢谢

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

工具/软件:

您好、

我正在运行 TMDS64EVM 电路板。 我处于 SBL 阶段、没有操作系统。

我正在初始化 DDR。

我发现在整个引导过程中、“DDR 使能时钟“需要 700ms。

问题。 这个计时是否合理、是否有绕过的方法?

您好、

这是启动日志。