主题中讨论的其他器件:AM69A

工具/软件:

您好:

我们正在使用模型导入工具。

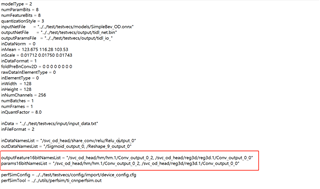

在 tidl_config 文件中、我们将两个卷积层添加到 outputFeature16bitNamesList 和 params16bitNamesList、如下图所示:

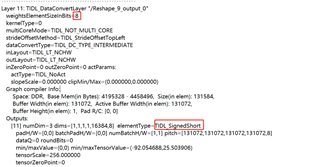

运行 model_import.sh 后、SimpleBev_OD.txt 第 11 层中仍然有 8 位、并且在运行演示 (../hirain、tidl_immation_app.out input.bin 2 1 1 SimpleBev_OD_io.bin SimpleBev_OD_Net.bin) 时会发生错误、如下图所示:

e2e.ti.com/.../0701-128x128-exracted.zip

e2e.ti.com/.../0701-128x128-exracted.zip

所有相关数据和图像都放置在压缩包中。

您能帮助检查哪里可能出错吗? (SDK 11.00 版)

谢谢