主题中讨论的其他器件:PCA9306、 AM6442

工具/软件:

您好、

我使用的是 AM6204、因此想澄清一些外设输入压摆率规格。

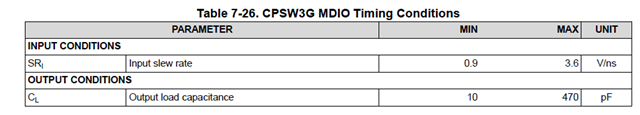

- 在我的器件中、MDIO 的实际测量输入压摆率为 0.14V/ns、这 不在 表 7-26 中指定的 0.9V/ns ~ 3.6V/ns 范围内。 CPSW3G MDIO 时序条件。 我的应用中 MDIO 的最大数据速率仅为 625kHz。

- 表 7-26 中的输入压摆率规格是否适用于更高的数据速率(例如仅限 5MHz)?

- 我是否可以为我的应用参考 7.8.6 LVCMOS 电气特性中的输入压摆率? 例如、输入压摆率规格= 33fV/ns = 0.0206V/ns?

2.对于 SPI 数据输入、 实际测得的输入压摆率为 1.45V/ns 、这不在 表 7-74 中规定的 2V/ns ~ 8.5V/ns 范围内。 MCSPI 时序条件。我的应用中 SPI 的最大数据速率仅是 10MHz。 同样、我是否可以 为应用参考 7.8.6 LVCMOS 电气特性中的输入压摆率? 例如、输入压摆率规格= 33fV/ns = 0.33V/ns?

对于 增强型捕获 (ECAP) 输入、实际测量的输入压摆率为 0.04V/ns 、不在表 7-45 规定的 1V/ns ~ 4V/ns 范围内。 eCAP 时序条件。 对于我的应用、ECAP 的最大数据速率仅为 1Hz。 同样、我是否可以 为应用参考 7.8.6 LVCMOS 电气特性中的输入压摆率? 例如、输入压摆率规格= 3.3MV/s?

4.对于 GPIOx、在我的应用中、切换频率低于 10kHz。 我是否可以 为我的应用参考 7.8.6 LVCMOS 电气特性中的输入压摆率? 例如、输入压摆率= 3.3MV/s?

表 7-59 中有另一种 GPIO 时序规格。 GPIO 时序条件、这是否仅适用于高切换频率应用? 功能时钟周期的值是多少?

5、 如果输入压摆率规格不符合,会有什么影响?