工具/软件:

你(们)好

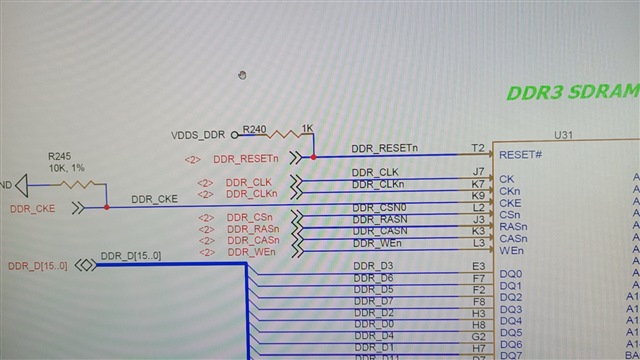

客户正在检查 该 DDR_RESETn 电阻是否有任何要求。

该电阻器必须是上拉电阻器还是下拉电阻器? 该电阻的值是多少、有任何建议?

谢谢

Zekun

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

您好、James

现在、客户遇到了大规模生产项目的一个紧急问题、想检查从 AM3352 到 DDR 的复位信号 RESETN 输出背后的逻辑是什么? 上电后的先决条件是什么?

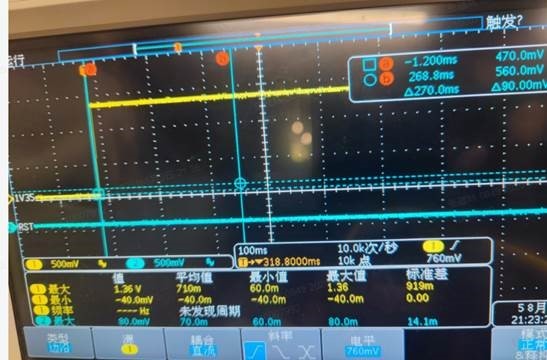

注意:DDR 部分使用 1.35V 电源。 两个原型当前的该信号卡在低电平而未被拉至高电平。 用新的 CPU 和 DDR 更换 CPU 和 DDR 尚未解决问题。 我还确认了用于此信号的两个焊盘之间的连接正常工作。 可能的原因是什么?

异常:

正常:

此致

Zekun

注意:DDR 部分使用 1.35V 电源。 两个原型当前的该信号卡在低电平而未被拉至高电平。 用新的 CPU 和 DDR 更换 CPU 和 DDR 尚未解决问题。 我还确认了用于此信号的两个焊盘之间的连接正常工作。 可能的原因是什么?

异常:

[/报价]嗨、Zekun

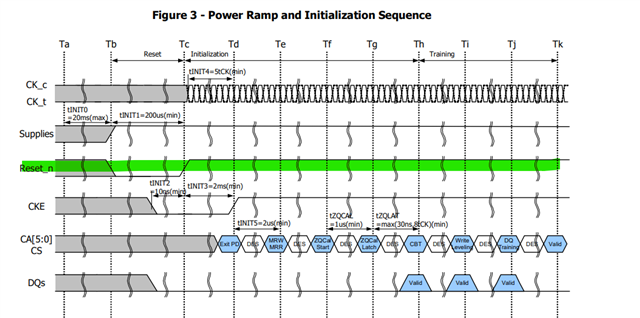

DDR 复位信号为高电平、将下拉短时间、然后再次上拉、从而复位 DDR

如果 DDR_RSTn 始终下拉、则可能是由硬件板中的某些元件故障引起的、例如电路中的电容器。

如果只有一个或两个硬件板有问题、请让客户检查电路板中的元件

此致

Semon