Other Parts Discussed in Thread: AM6422

工具/软件:

你(们)好

AM6422 具有一个 16b DDR4 @800MHz。

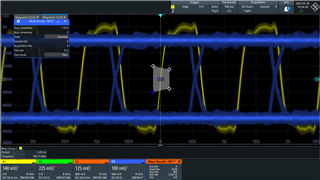

我们会看到 CA 信号和 CS 信号之间的延迟(CS 延迟)、请参阅随附的测量结果。

是否可以单独调整 CS 以优化设置/保持?

此致、

基督教

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

尊敬的 Christian:

好的、同意。 是来自两个不同电路板的两个不同示波器屏幕截图、还是同一电路板的两个不同引导? 我想知道这是否是培训问题。 我认为从另一个帖子请求的寄存器转储在这里会有所帮助。

此外、只需确认 在设计过程中是否考虑了此处布局指南 (www.ti.com/.../spracu1) 中的所有要求。

此致、

James