工具/软件:

您好!

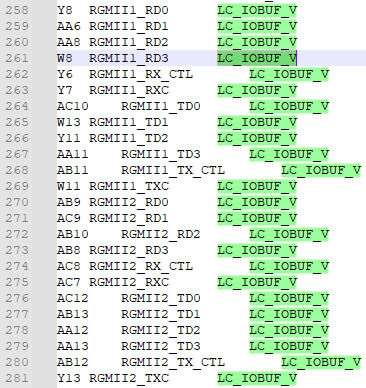

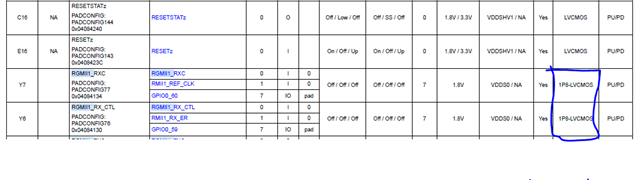

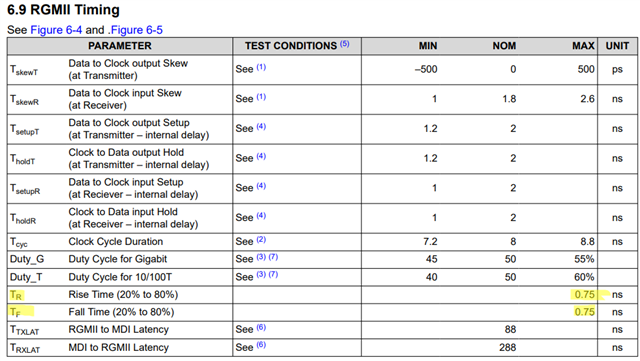

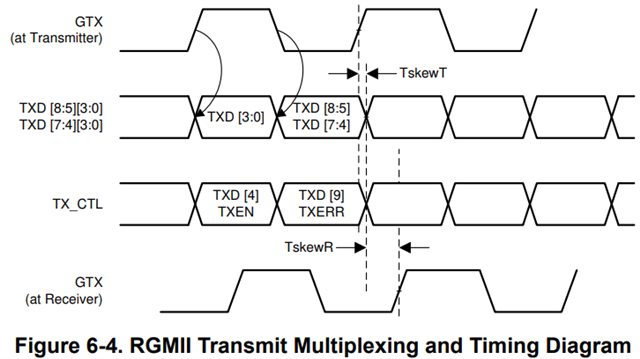

我对 AM62L 的集成有一个小问题。 我们目前正在验证过程中、但在这里我们看到了不符合定义的 RGMII 信号。

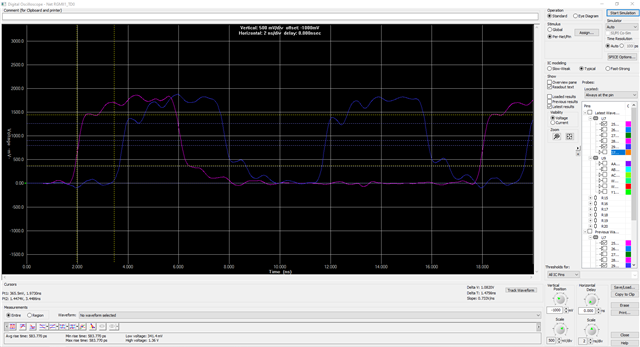

| 眼图 | 上升时间 | 下降时间 |

|---|---|---|

|

|

|

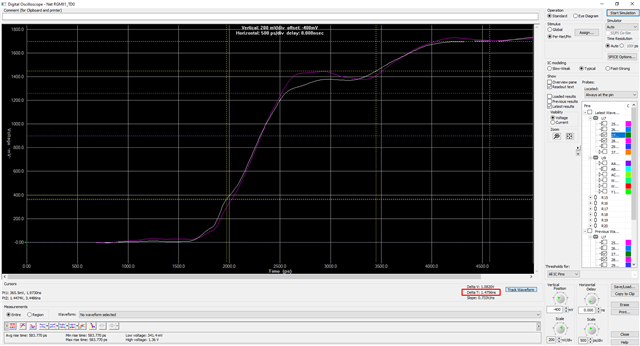

上升和下降时间超过 750ps。 phy 距离 SoC 仅约 3cm(布线长度)。 我们做了一些模拟,并发现,一个串联端接 60R 为了匹配它与我们的测量,但目前没有使用串联端接。

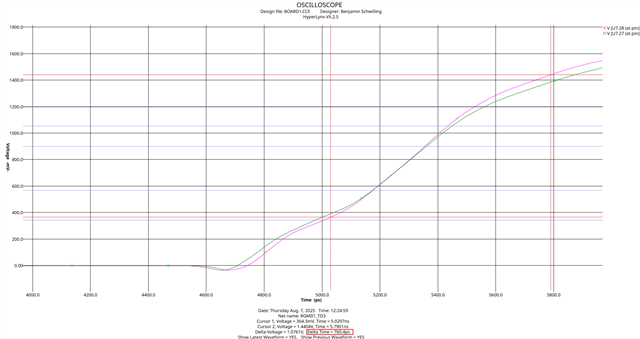

使用 TI 网站上 AM62L 和 DP83867IRRGZ 的 IBIS 模型仿真中的相同迹线实现了 760.4ps 的时间、偏差有点大、但如果能做到这一点、我会很高兴。

我们使用的软件是 Mentor Hyperlynx。

我的问题是、仿真与现实世界有何不同? 我们尝试调整仿真、如果插入 60R 串联终端、则只获得匹配的结果。 改进非常大。

IBIS 模型可能有故障吗? 您是否通过实际测量验证了这些模型?

谢谢、

我