工具/软件:

平台详细信息:

-

处理器: TDA4VM(定制板)

-

Linux SDK:

ti-processor-sdk-linux-j7-evm-08_01_00_07 -

RTOS SDK:

ti-processor-sdk-rtos-j721e-evm-08_01_00_13

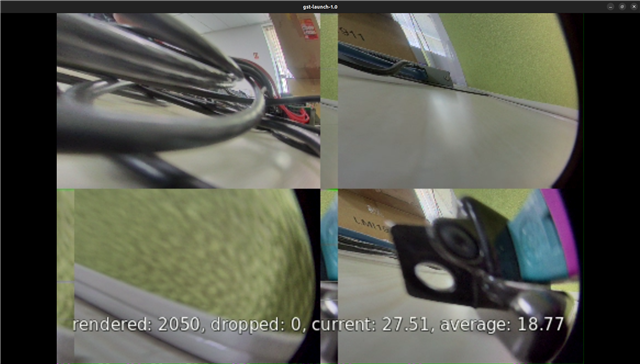

我们使用基于 TDA4VM 的定制电路板和多摄像头应用(生产者-消费者)。 在修改流水线以通过子采样降低分辨率时、我们发现了一个问题 摄像机通道 2、3 和 4 中出现镜头环伪影 在实时四屏显示期间。 单视图适用于所有摄像头。

流水线详细信息:

初始(工作)流水线:

capture --> VISS (1936x1220) --> Shared Memory (Producer) -->

Shared Memory (Consumer) --> LDC (1920x1080) -->

Scaler (480x320) --> Mosaic

已修改(观察到问题)流水线:

capture --> VISS (1936x1220) --> Subsample (÷2 --> 960x608) -->

Shared Memory (Producer) --> Shared Memory (Consumer) -->

LDC (960x608) --> Scaler (480x320) --> Mosaic

发现的问题:

-

在修改后的流水线中、摄像头通道 2、3 和 4 的输出中会出现镜头环伪影。

-

摄像机 1 似乎不受影响。

-

我们怀疑这可能与使用为生成的 LDC LUT 有关 1920x1080 而新分辨率为 960x608. 。

问题:

-

由于 LDC LUT 分辨率与输入图像尺寸不匹配、观察到的镜头环问题是否存在?

-

我们是否需要专门针对新分辨率 (960x608) 重新生成 LUT?

-

是否有任何指南或工具可用于为自定义分辨率生成 LDC LUT?

-

是否有任何特定于多摄像头通道(摄像机 2/3/4)的影响或考虑因素会导致此伪影?

感谢您提供有关如何解决此问题并确保在下采样分辨率下正确校正失真的指导。

谢谢你。