工具/软件:

您好!

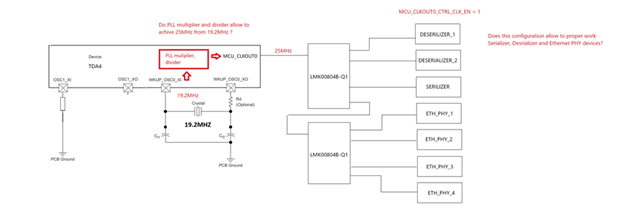

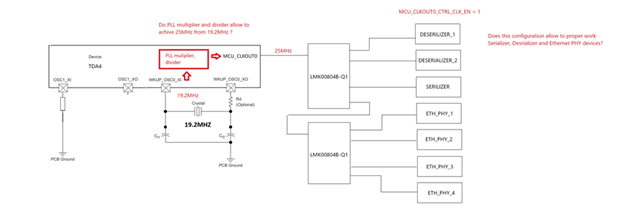

数据表指定 MUC_CLKOUT0 用于以太网 PHY。 如果我们使用这个公鸡作为解串器的参考时钟、它会影响 RGMII 通信吗? 以下是时钟方案。

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

工具/软件:

您好!

数据表指定 MUC_CLKOUT0 用于以太网 PHY。 如果我们使用这个公鸡作为解串器的参考时钟、它会影响 RGMII 通信吗? 以下是时钟方案。

嗨、Daviel、

时钟输出可用于以太网 PHY、但是、必须由客户验证时钟的性能、以确保其满足其系统要求。

有太多变量会影响抖动、因此我们不会在数据表中定义时钟的性能。 一个示例是实现所需频率所需的器件参考时钟频率与 PLL 配置的组合、其中、如果 PLL 配置为在整数模式与小数模式下运行、甚至是在不同的 M/N 值下运行、抖动可能会显著不同。 另一个示例是客户 PCB 上的 PLL 电源噪声会影响抖动。

这些系统级依赖项因具体实现而异。 因此、我们告诉客户、只要客户验证时钟输出的性能符合所连接器件的要求、他们就可以使用时钟输出。