Other Parts Discussed in Thread: AM67A, LMK3H0102, J722SXH01EVM

主题中讨论的其他器件:AM67A、 LMK3H0102、

工具/软件:

您好、

客户将尝试为 PCIe 使用外部基准时钟源(AM67A 的“SERDESx_REFCLKx_P/N “引脚)。

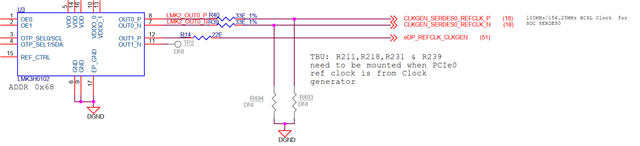

他们将参考 EVM 原理图了解建议的电路。 您未在最新 EVM (PROC170E3B) 上实施外部时钟 (LMK3H102)、但我们知道您已在之前的 EVM 上实施了该时钟器件(现在我们称为“PROC170E1")“)。

查看之前的 EVM 原理图时、您已经在时钟线上实现了 33 Ω 串联电阻器 (R40、R39)。

他们将计划在其定制电路板上使用与 EVM 相同的器件 (LMK3H102)。

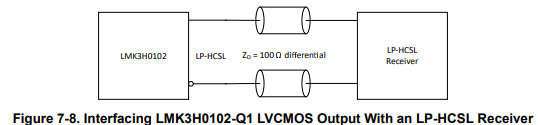

(时钟源的输出设置将为“LP-HCSL"。“。 可能与 EVM 相同。)

我有以下问题。

*我们是否需要在参考时钟线路上实现“33 欧姆“串联电阻?

(我认为这些电阻用于阻尼电阻,但如果可能,请说明这些电阻的作用以及您如何确定阻尼电阻的值。)

此致、