Thread 中讨论的其他器件:SK-AM69、 TDA4VH、 AM69

工具/软件:

我们的定制 电路板 PCIe 根 配置如下:

PCIE0 (SERDES1 LANE0 LANE1 Lane2 LANE3)、

PCIE1 (SERDES0 LANE0/LANE1)

PCIe3 (SERDES0 通道 2/LANE3)

FPGA 3 侧端口为 PCIe EP。

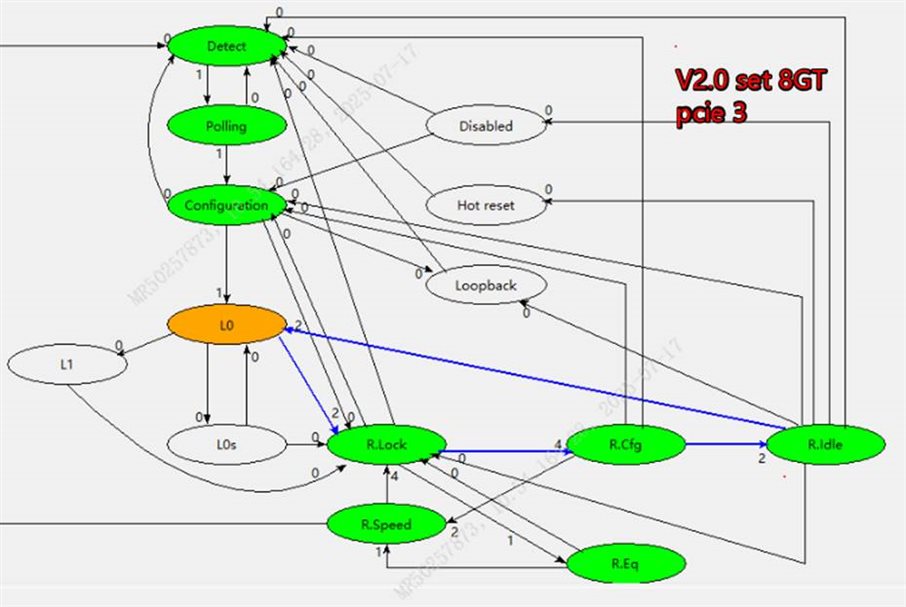

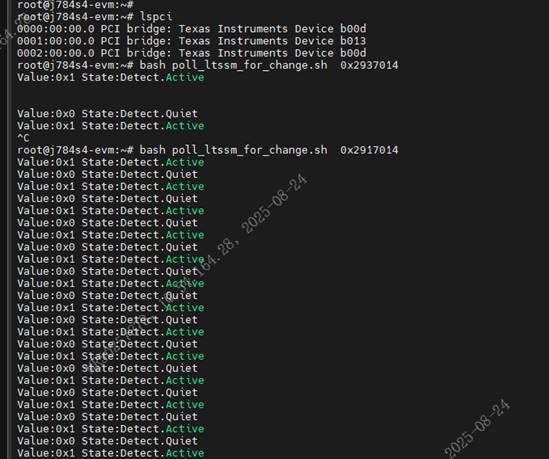

当连接 3 个 EP (FPGA) 并以 8GT/s 的速率配置时、无法识别 PCIe3、可以识别 PCIE0/PCIE1 并以 8GT/s 的速率运行

当 3 个 EP 配置为 5GT/s 时、所有这些都可以被识别并以 5GT/s 的速率运行。

如果仅 连接 PCIe 并以 8GT/s 的速率配置 EP、则可以识别 PCIe3、但仅以 2.5GT/s 的速率运行

问题:PCIE1 和 PCIe3 能否 在一个 Serdes0 上同时以 8GT/s 的速度运行?